Layout structure and formation method of semiconductor integrated circuit device

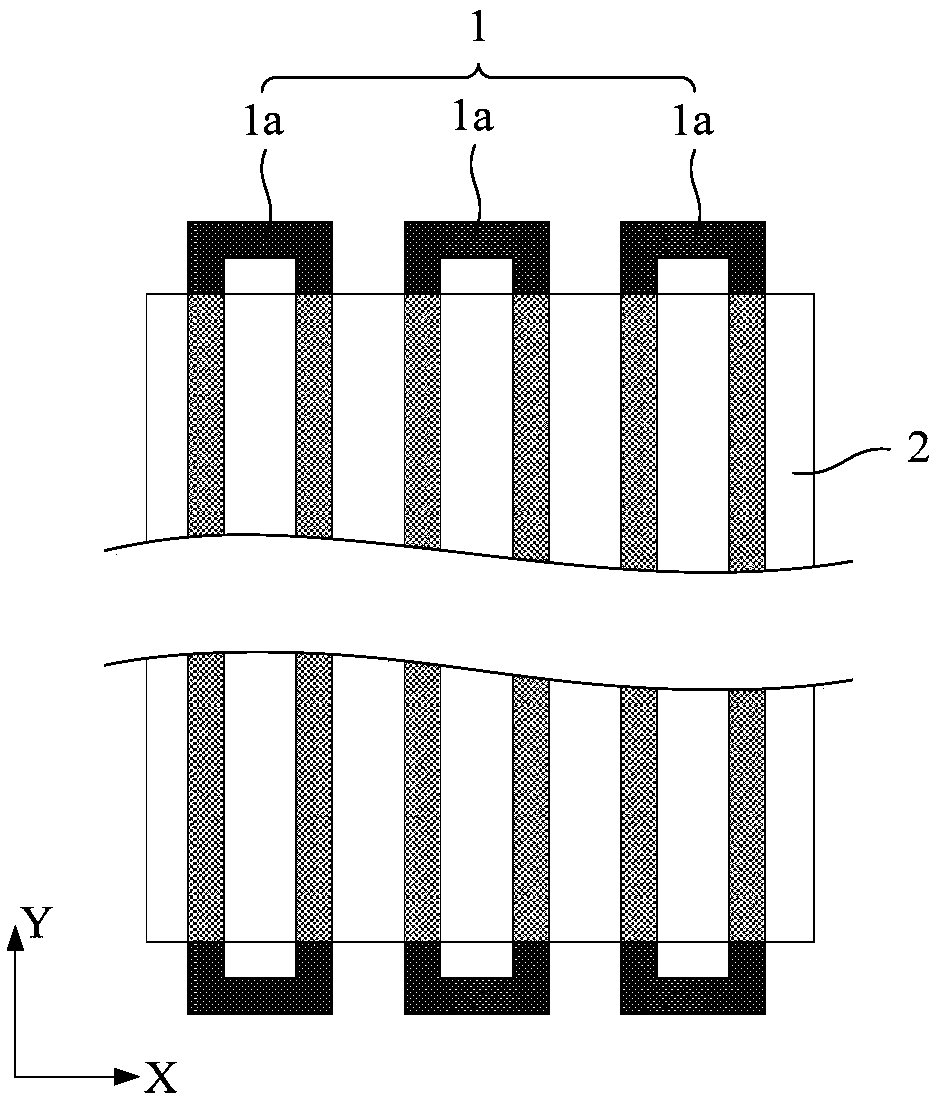

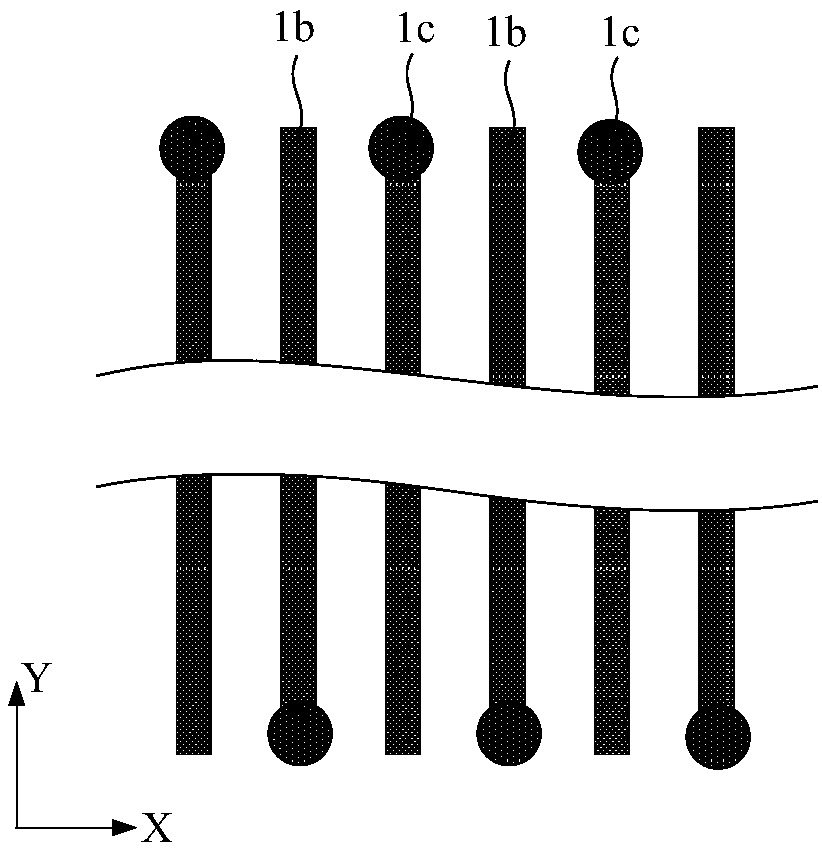

A technology of layout structure and integrated circuit, which is applied in semiconductor/solid-state device manufacturing, circuits, electrical components, etc., and can solve the problems of large contact resistance, small distance, and difficult preparation of node contact layer 1c.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

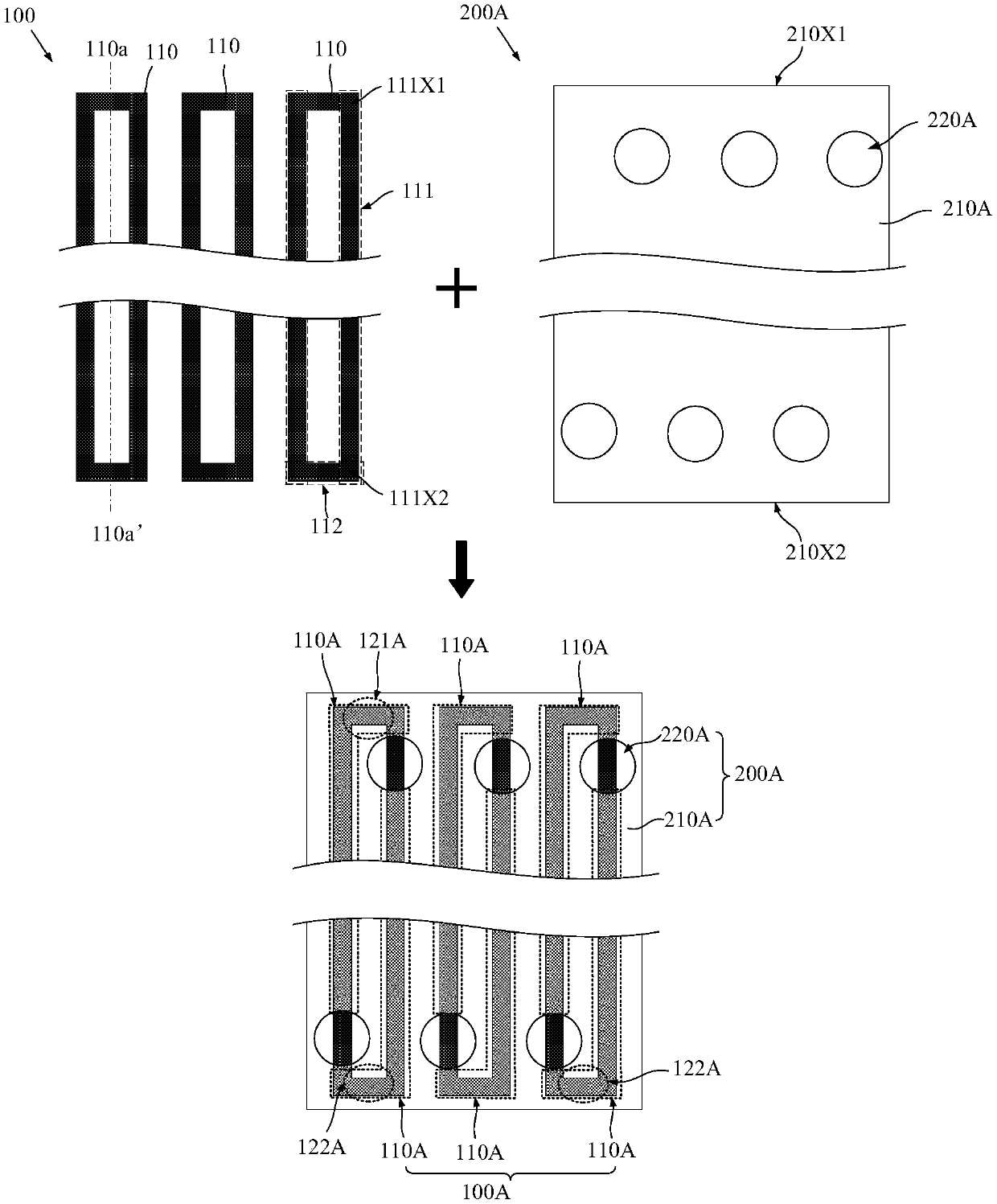

[0113] figure 2 It is a schematic diagram of the layout structure in Embodiment 1 of the present invention, such as figure 2 As shown, the layout includes:

[0114] A first pattern of features 100 comprising at least one first sub-pattern; and,

[0115] The mask pattern 200A has a cover pattern area 210A and a plurality of truncated pattern areas 220A; the cover pattern area 210A has two opposite first borders 210X1 and second borders 210X2 in the second direction (Y direction), the Both the first boundary 210X1 and the second boundary 210X2 extend along the first direction (X direction); and, a plurality of the truncated pattern areas 220A are respectively arranged in regions close to the first boundary 210X1 and the second boundary 210X2.

[0116] It can be understood that, in the photolithography process, the mask pattern area 210A of the mask pattern 200A covers the part that does not need to be exposed, and the cut-off pattern area 220A exposes the part that needs to ...

Embodiment 2

[0147] Figure 4 It is a schematic structural diagram of the layout structure in Embodiment 2 of the present invention. combine figure 2 and Figure 4 As shown, the difference between this embodiment and the first embodiment is that the truncated pattern area of the mask pattern is a non-closed truncated pattern area.

[0148] Such as Figure 4 As shown, the first characteristic pattern 100 in this embodiment has a plurality of annular sub-patterns 110 . And, in the mask pattern 200B, the truncated pattern area 220B is located on the first boundary 210X1 or the second boundary 210X2 of the covering pattern area 210B, and is separated from the first boundary 210X1 or the second boundary 210X2. The boundary 210X2 extends toward the center of the covered graphic area 210B, so that the truncated graphic area 220B is embedded into the covered graphic area 210B from the first boundary 210X1 or the second boundary 210X2. The truncated graphic areas 220B communicate with each ...

Embodiment 3

[0161] In this embodiment, the truncated pattern area of the mask pattern is also a non-closed truncated pattern area. And compared with the second embodiment, the truncated pattern area in this embodiment further exposes all the connection parts of the ring sub-patterns.

[0162] Figure 6a It is one of the structural schematic diagrams of the layout structure in Embodiment 3 of the present invention, such as Figure 6a As shown, in the mask pattern 200C, each of the truncated pattern regions 220C exposes the end of one of the lines 111 of the annular sub-pattern 110, and the plurality of truncated pattern regions 220C are far away from the mask pattern region. One side communicates with each other and further exposes all the connection portions 112 of the annular sub-pattern 110 . That is, the masking pattern area 210C of the mask pattern 200C only covers the lines 111 of the annular sub-pattern 110 , so that the strip-shaped sub-pattern 110C in the second feature patter...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com