Transistor structure with double buried oxide layers and preparation method thereof

A technology of double buried oxide layer and buried oxide layer, which is applied in the direction of transistors, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve the problems that high-resistance substrates and back gate voltage functions cannot be shared, difficult high-performance radio frequency circuits, etc. Achieve the effects of harmonic suppression and crosstalk noise suppression, high radio frequency characteristics, and electrical performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The present invention will be further described below in conjunction with specific embodiments. It should be understood that the following examples are only used to illustrate the present invention but not to limit the scope of the present invention.

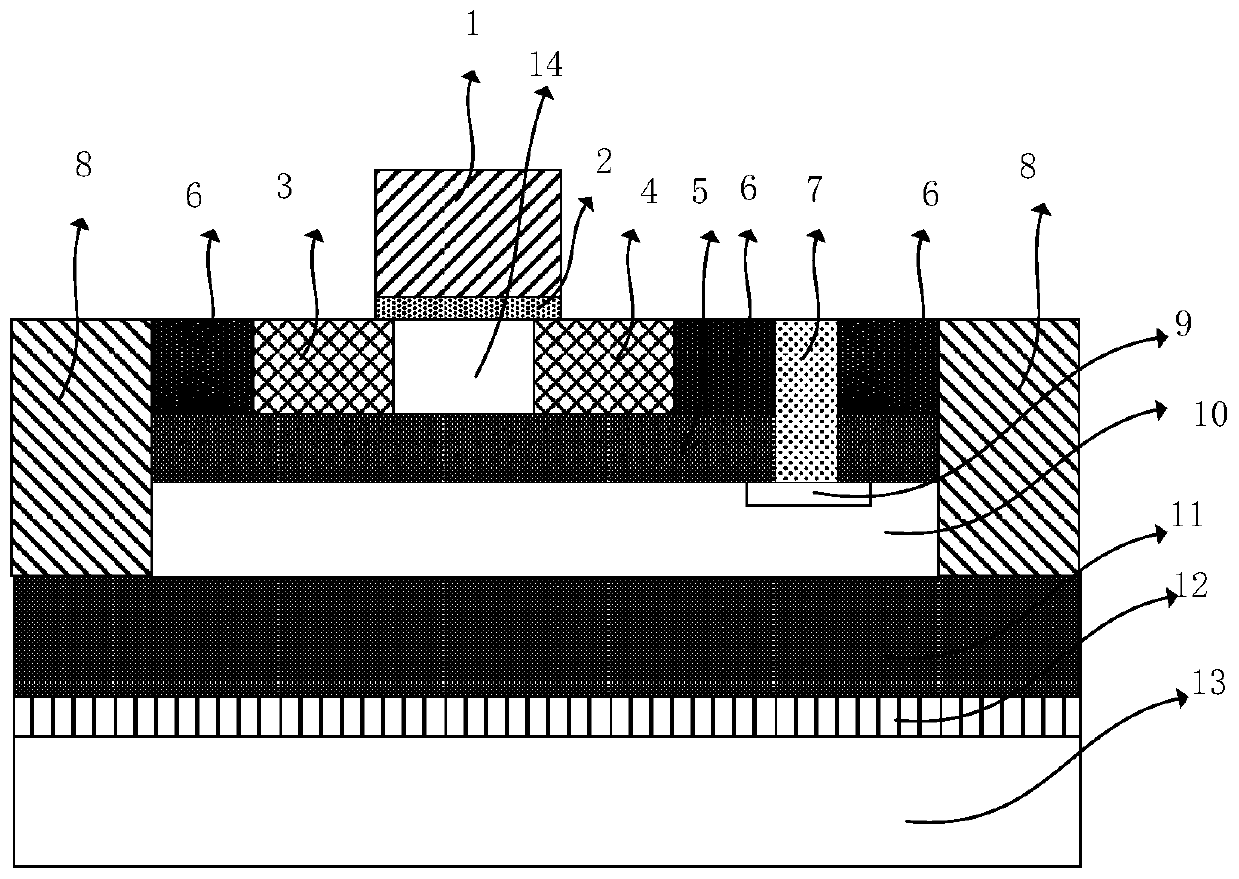

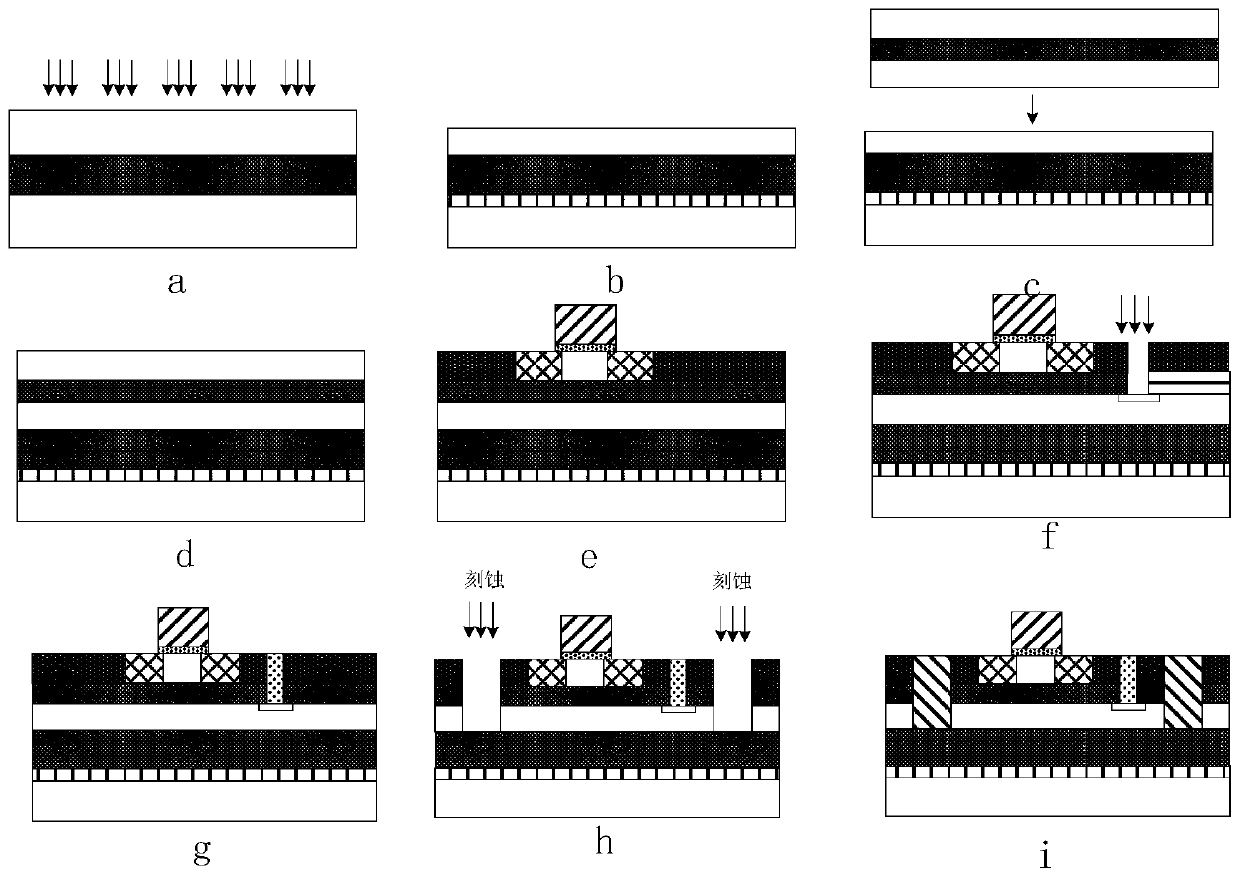

[0022] According to a preferred embodiment of the present invention, a transistor structure 100 with a double buried oxide layer is provided, such as figure 1 As shown, the transistor structure 100 includes in order from top to bottom: a top silicon layer 14, a gate 1 located above the top silicon layer 14, a gate dielectric layer 2, a source 3 and a drain 4 located at both lateral ends of the top silicon layer 14 , the shallow trench isolation region 6 located at the outer end of the active region; the first buried oxide layer 5 ; the second silicon layer 10 ; the second buried oxide layer 11 ; the defect layer 12 ; Wherein, the transistor structure 100 also includes a via hole 7 that sequentially penetrates the shallow...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More