Packaging structure and packaging method of multilayer chip

A packaging structure, multi-layer chip technology, applied in electrical components, electrical solid devices, circuits, etc., can solve the problems of inability to realize the electrical measurement of each layer of chips, inconvenient rework, etc., to reduce manufacturing costs, improve product yield, and simplify The effect of the operation steps

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

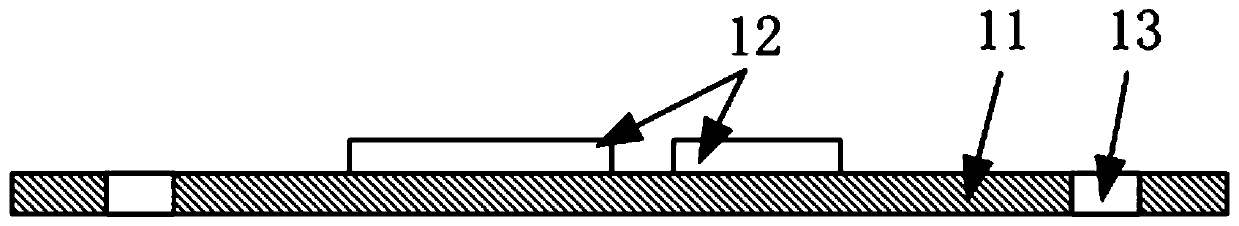

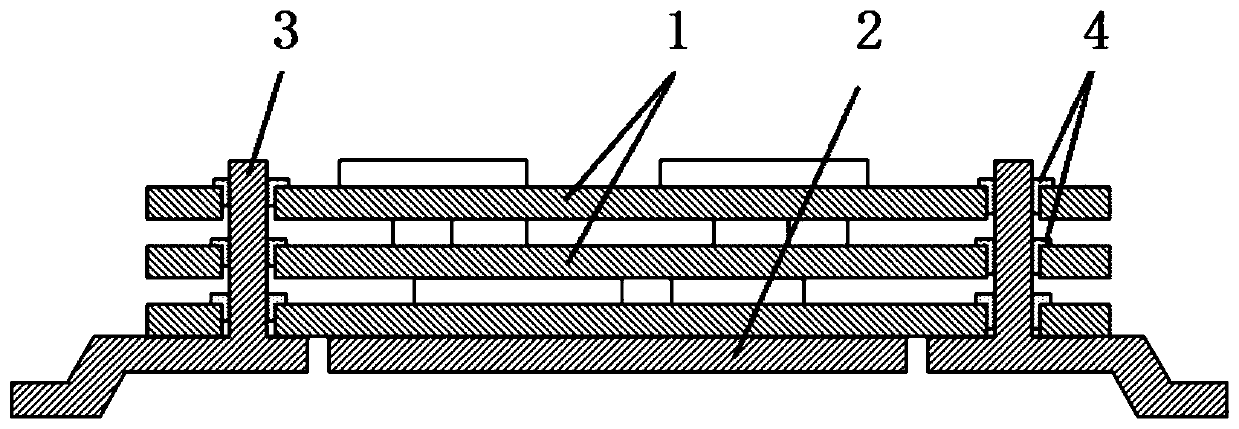

[0039] A packaging structure for multi-layer chips, such as figure 1 and figure 2 As shown, it includes a metal frame 2 , several column connectors 3 and several chip components 1 . Wherein, a number of chip components 1 are stacked sequentially above the metal frame 2 from top to bottom, and the bottom ends of the columnar connectors 3 are fixed on the upper surface of the metal frame 2 . Each chip assembly 1 includes a substrate 11, a chip unit 12 connected to the substrate 11, and a plurality of through holes 13 arranged on the substrate 11, such as figure 1 shown. In the present invention, the number of columnar connectors 3 is greater than or equal to the type of signal output of the chip component 1 in the packaging structure, and the position corresponding to each columnar connector 3 on the substrate 11 is provided with a through hole 13 for the penetration of the columnar connector 3 , Each columnar connector 3 can be connected to a chip component 1 with the same ...

Embodiment 2

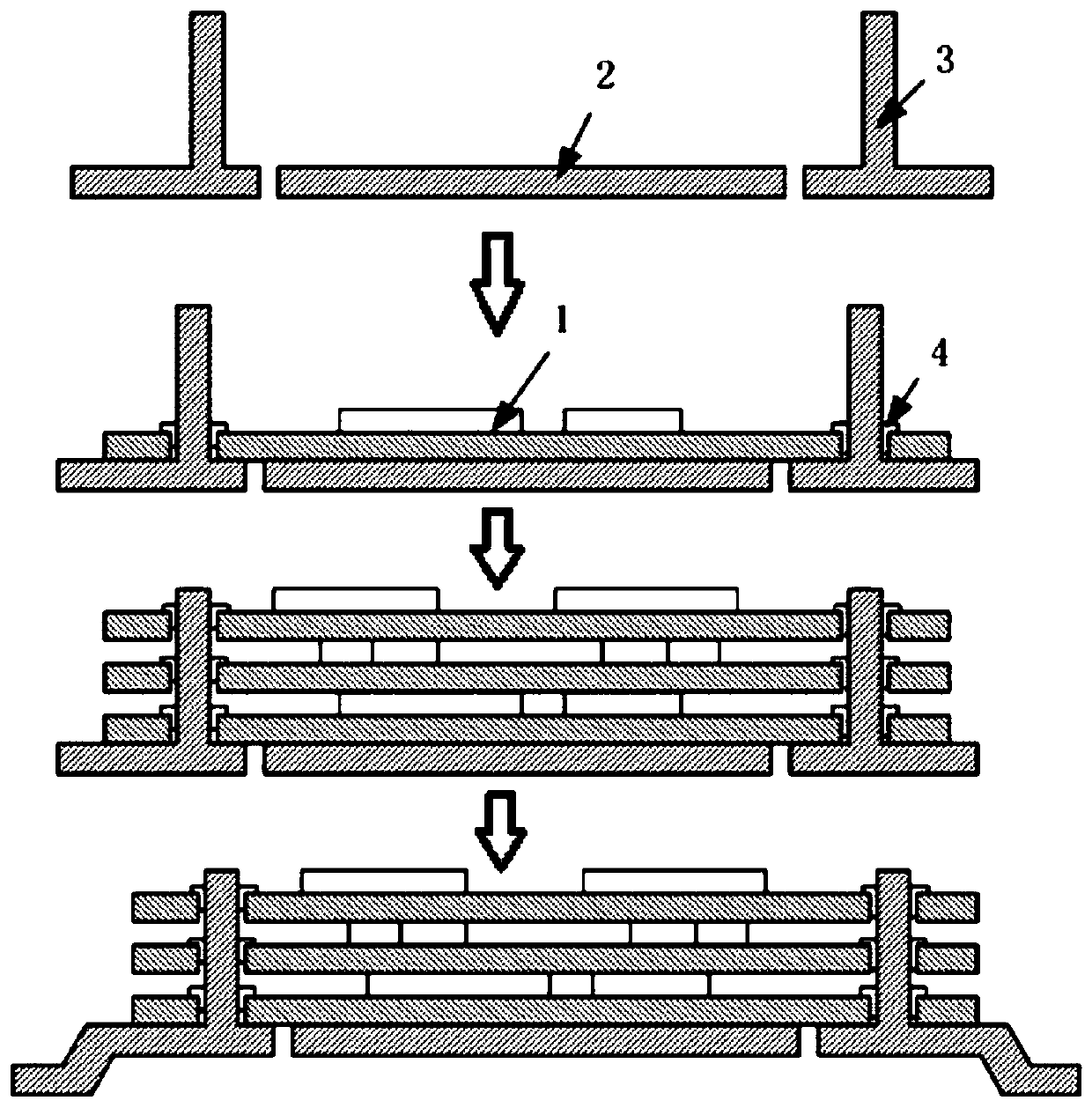

[0043] This embodiment provides a packaging method for a packaging structure of a multilayer chip, such as image 3 As shown, the specific process is as follows:

[0044] Step 1, preparing the metal frame 2 and several chip components 1 .

[0045] When the metal frame 2 is prepared, first fix the columnar connector 3 on the upper surface of the metal frame 2 according to the number of signal types output by a number of chip components 1 that need to be integrated, such as: a number of chip components 1 output When there are two signal types, no less than two columnar connectors 3 are set on the upper surface of the metal frame 2. In this embodiment, two columnar connectors 3 are set as an example, as image 3 shown;

[0046] When several chip components 1 are prepared, the preparation method of each chip component 1 is the same, and the chip monomer 12 is connected on the substrate 11, and a plurality of through holes 13 are arranged on the substrate 11 to obtain the chip co...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More