Ethernet self-adaption method, device and system based on FPGA

An Ethernet and adaptive technology, applied in transmission systems, digital transmission systems, network interconnection, etc., can solve the problems of weak stability, poor adaptability, and inflexibility of using dedicated interfaces for three-speed Ethernet adaptive technology, and achieve Improve application applicability, easy application and strong portability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

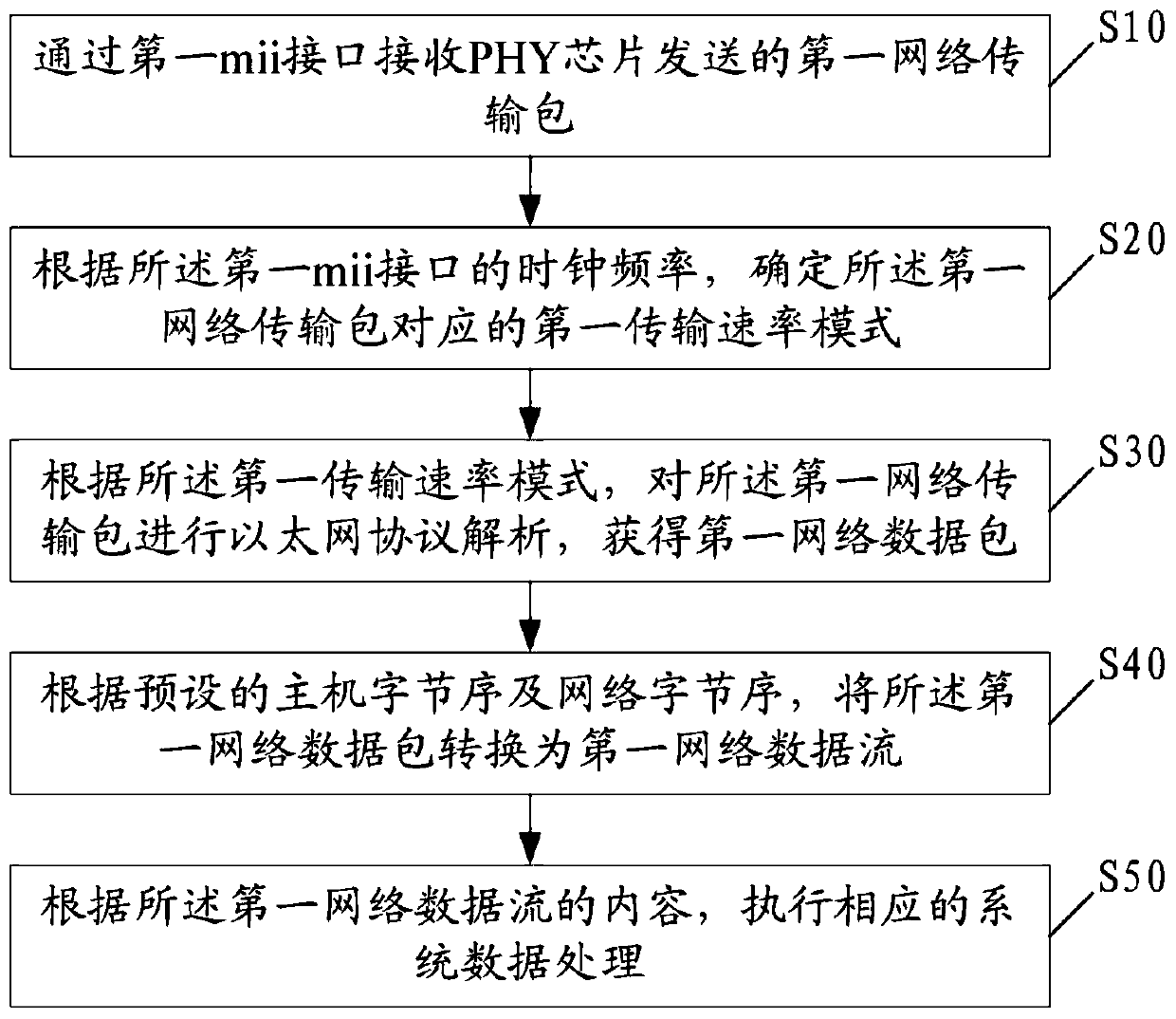

[0042] figure 1 Shown is a schematic flowchart of the FPGA-based Ethernet self-adaptation method according to Embodiment 1 of the present invention.

[0043] Such as figure 1 As shown, the method includes the following steps:

[0044] S10: Receive the first network transmission packet sent by the PHY chip through the first mii interface;

[0045] S20: Determine the first transmission rate mode corresponding to the first network transmission packet according to the clock frequency of the first mii interface;

[0046] Specifically, the 10M broadband Ethernet transmission mii interface clock is 2.5M, each clock transmits 4bit data, two clocks transmit 8bit data, that is, 1byte data; the 100M broadband Ethernet transmission mii interface clock is 25M, each clock 4bit data is transmitted, two clocks transmit 8bit data, that is, 1byte data; 1000M broadband Ethernet transmission mii interface clock is 125M, each clock transmits 8bit data, and the rising edge and falling edge of th...

Embodiment 2

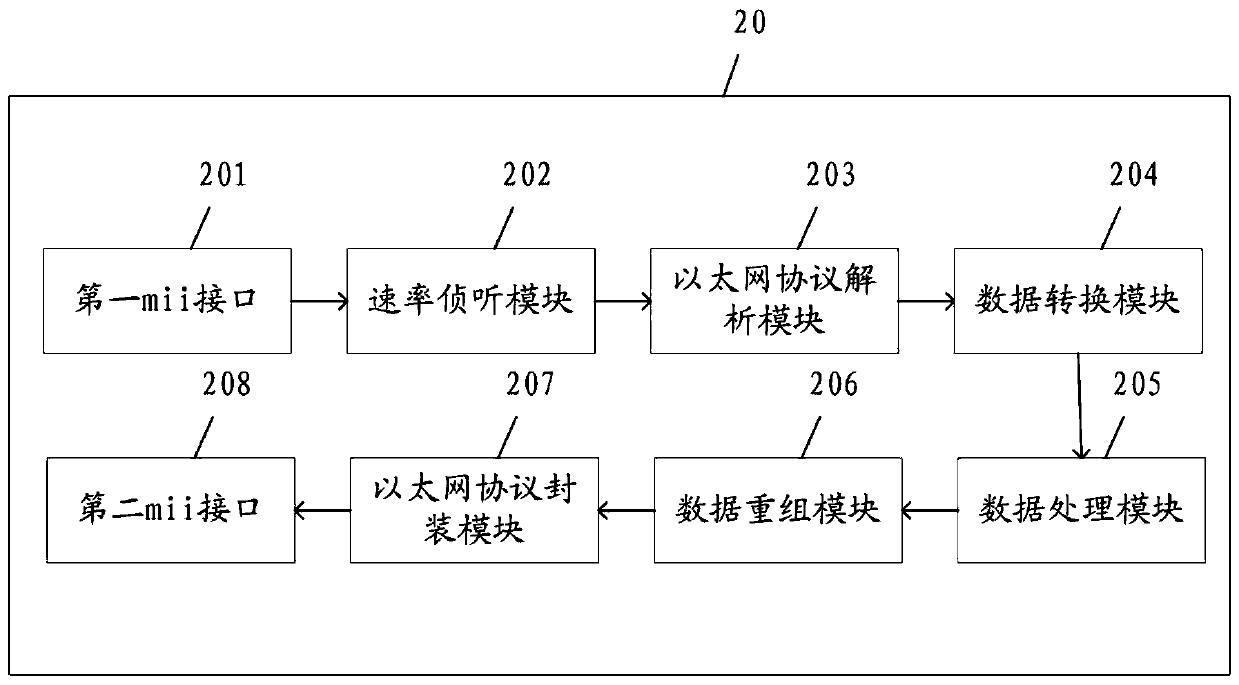

[0062] figure 2 Shown is a schematic structural diagram of an FPGA-based Ethernet adaptive device according to Embodiment 2 of the present invention.

[0063] Such as figure 2 As shown, the device includes: a first mii interface, a rate monitoring module, an Ethernet protocol analysis module, a data conversion module and a data processing module, wherein,

[0064] The first mii interface is used to receive the first network transmission packet sent by the PHY chip;

[0065] Wherein, the first mii interface can be any one of rgmii interface, rmii interface, smii interface, ssmii interface, gmii interface or sgmii interface. Compared with the data transmission interface in the prior art, the inherent function chip has been defined. Dedicated interface, the data transmission interface in Embodiment 2 of the present invention is more flexible in selection.

[0066] The rate listening module is used to determine the first transmission rate mode corresponding to the first netwo...

Embodiment 3

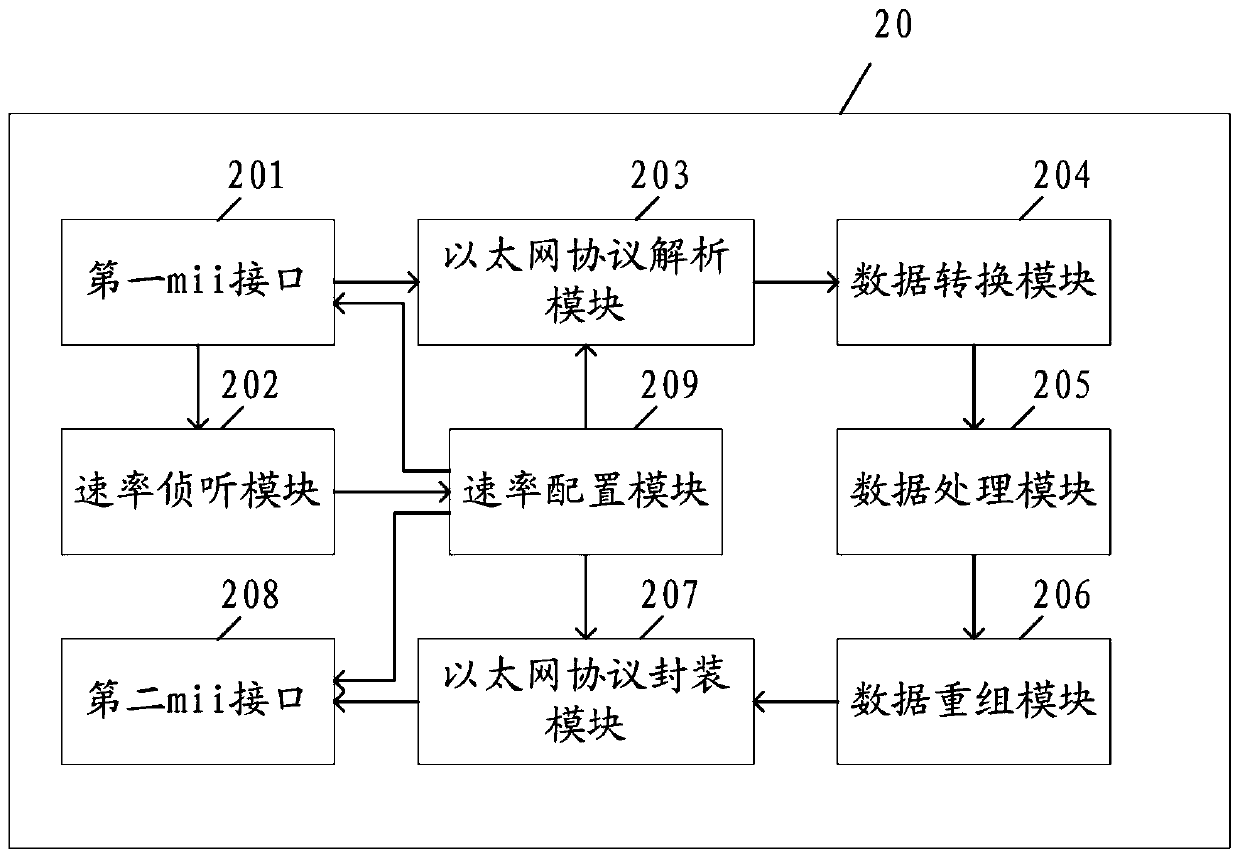

[0083] image 3 Shown is a schematic structural diagram of an FPGA-based Ethernet adaptive device according to Embodiment 3 of the present invention.

[0084] Preferably, the FPGA-based Ethernet adaptive device of embodiment three, on the basis of embodiment two, also includes a rate configuration module, and its structural diagram is as follows image 3 shown;

[0085] Its workflow is basically the same as that of Embodiment 2, and details will not be repeated here. The difference is that: after the rate monitoring module determines the first transmission rate mode corresponding to the first network transmission packet, the first transmission rate is set by the rate configuration module. The mode is configured to the first mii interface, the Ethernet protocol analysis module, the Ethernet protocol encapsulation module and the second mii interface, the first mii interface, the Ethernet protocol analysis module, the Ethernet protocol encapsulation module and the second mii int...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More