Large-bit-width high-performance adder structure based on FPGA

An adder, high-performance technology, applied in the field of high-performance adder structure, can solve the problems of the operation speed of the adder, increase the delay, long programmable interconnection, etc. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] In order to further clarify the purpose, technical solutions and advantages of the present invention, the present invention will be further described in detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

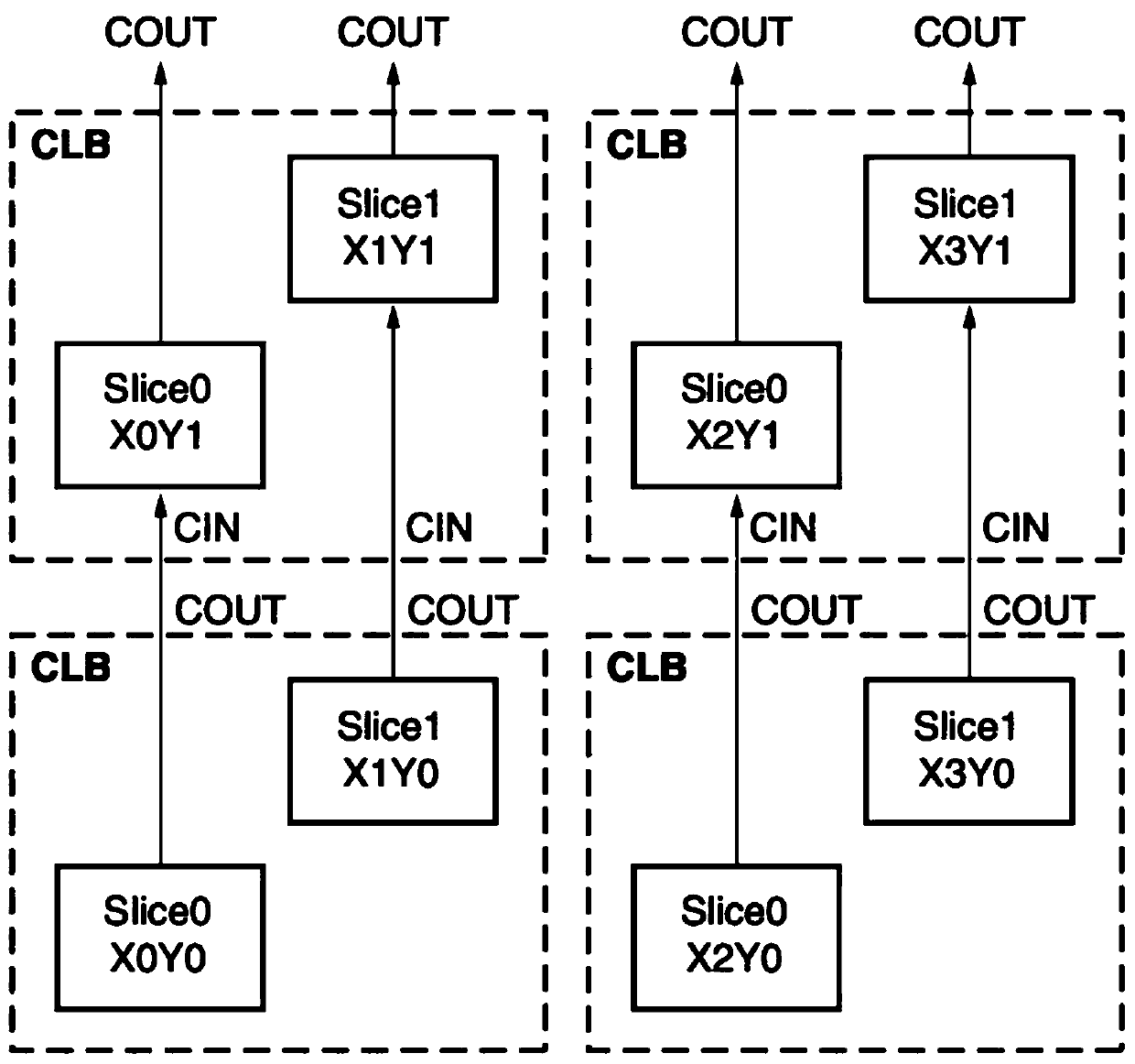

[0019] figure 1 It is a schematic diagram for illustrating the layout of the carry chain in the FPGA for the present invention. In Xilinx FPGA, the carry chain is embedded in the Slice of the configurable logic unit CLB, and two Slices form a configurable logic unit CLB. The input signal cin is input from the lower end of the Slice, and the output signal cout is output from the upper end. An adder with a bit width greater than 4 bits can be implemented by cascading carry chains in multiple Slices arranged in a column. It should be pointed out that the interconnection used for the carry chain cascading is dedicated, that is, the interconnection is different from the general programmable interconnection, it is only ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com