Positive feedback exclusive-OR/exclusive-OR gate and hybrid logic adder

A mixed logic and positive feedback technology, applied in logic circuits, exclusive-or circuits, logic circuits with logic functions, etc., can solve the problems of adder delay and power consumption delay product increase

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

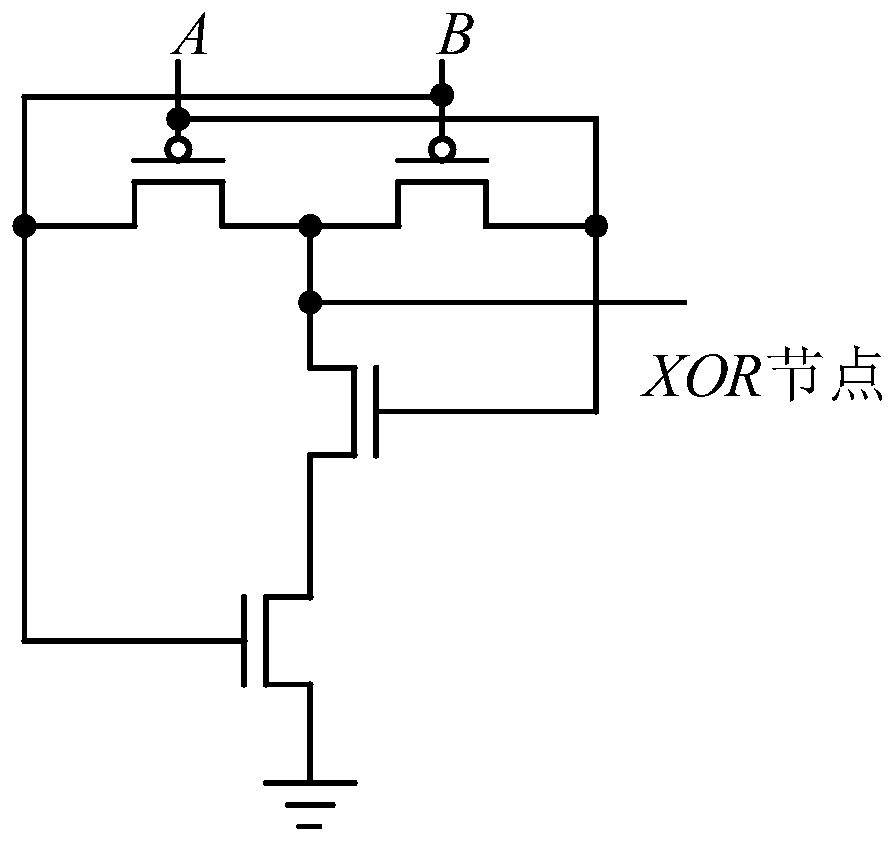

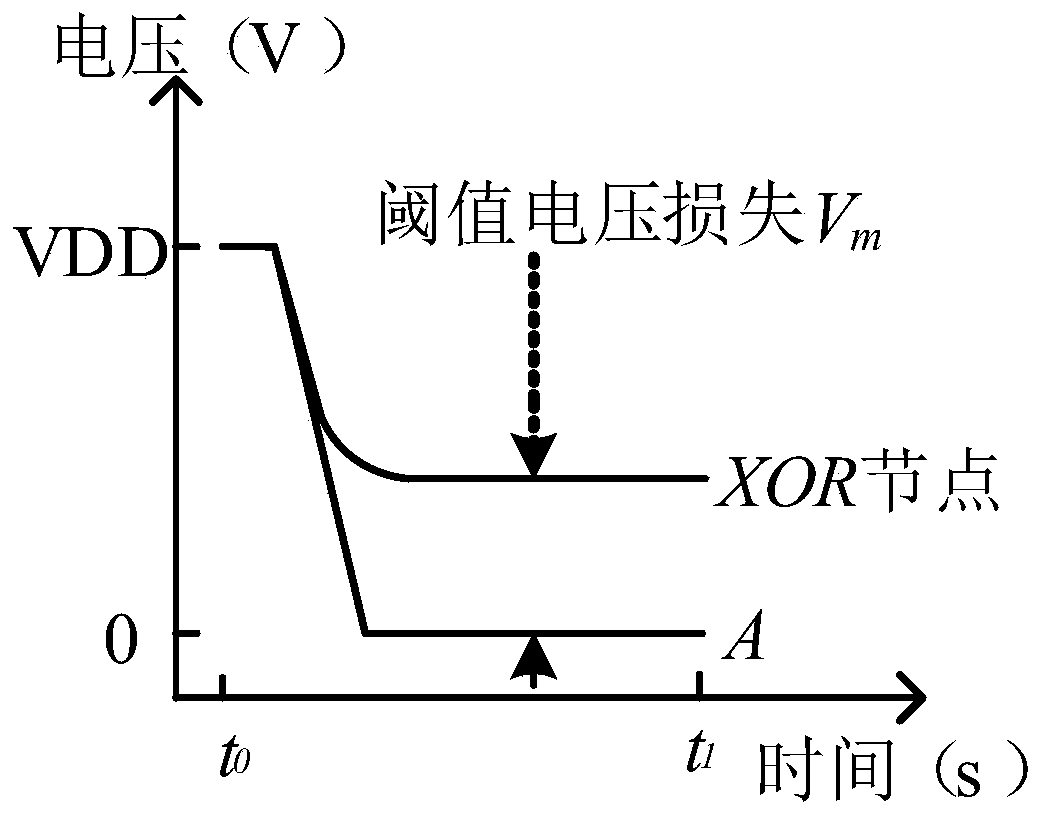

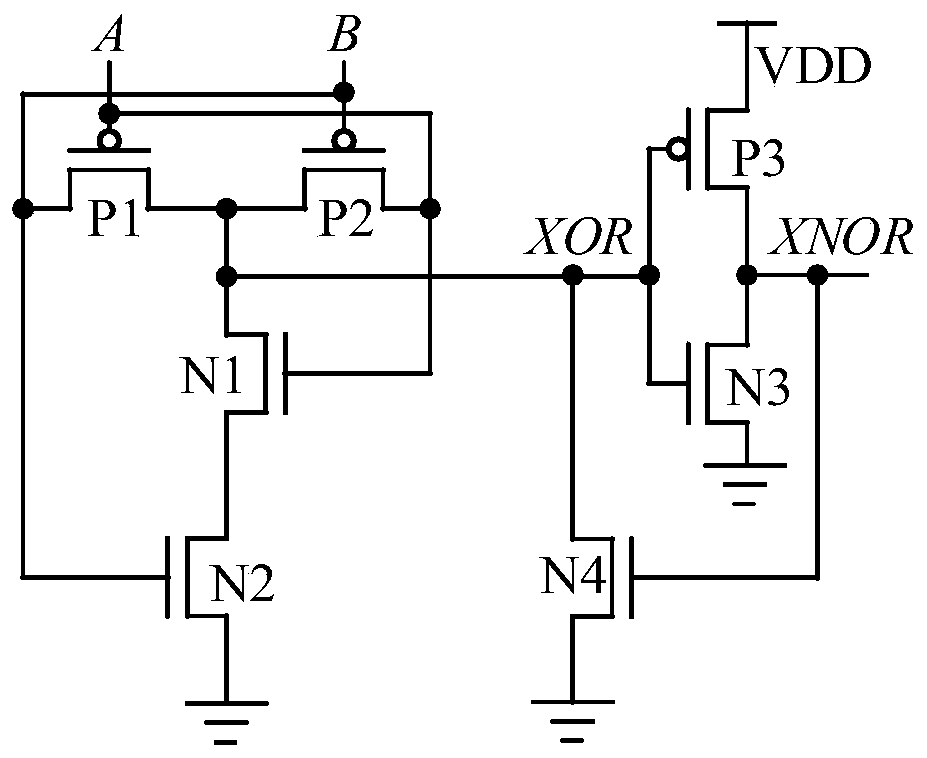

[0023] Example: such as figure 2 As shown, a positive feedback XOR / XOR gate includes a first PMOS transistor P1, a second PMOS transistor P2, a third PMOS transistor P3, a first NMOS transistor N1, a second NMOS transistor N2, and a third NMOS transistor N3 and the fourth NMOS transistor N4; the gate of the first PMOS transistor P1, the drain of the second PMOS transistor P2 are connected to the gate of the first NMOS transistor N1, and its connection terminal is the first positive feedback exclusive OR / exclusive OR gate Input terminal, the first input terminal of the positive feedback XOR / XOR gate is used to access the first input signal A, the source of the first PMOS transistor P1, the source of the second PMOS transistor P2, the first NMOS transistor N1 The drain, the gate of the third PMOS transistor P3, the gate of the third NMOS transistor N3, and the drain of the fourth NMOS transistor N4 are connected, and the connection terminal is the exclusive OR logic output termi...

Embodiment 1

[0026] Embodiment one: if Figure 5 and Figure 6 As shown, a mixed logic adder includes positive feedback exclusive OR / nor gate and an output circuit for outputting a sum signal and a carry signal for a high bit, and the positive feedback exclusive OR / nor gate has a first input terminal, a first Two input terminals, an exclusive OR logic output terminal and an exclusive OR logic output terminal, the output circuit has a first input terminal, a second input terminal, a third input terminal, a fourth input terminal, a first output terminal and a second output terminal, and the positive The first input end of the feedback XOR / XOR gate is used to access the first input signal A, the second input end of the positive feedback XOR / XOR gate is used to access the second input signal B, and the first input of the output circuit The input terminal is connected to the exclusive OR logic output terminal of the positive feedback exclusive OR / same OR gate, the second input terminal of the ...

Embodiment 2

[0027] Embodiment two: if Figure 7As shown, a mixed logic adder includes positive feedback exclusive OR / nor gate and an output circuit for outputting a sum signal and a carry signal for a high bit, and the positive feedback exclusive OR / nor gate has a first input terminal, a first Two input terminals, an exclusive OR logic output terminal and an exclusive OR logic output terminal, the output circuit has a first input terminal, a second input terminal, a third input terminal, a fourth input terminal, a fifth input terminal, a first output terminal and a second input terminal Two output terminals, the first input terminal of the positive feedback XOR / XOR gate is used to access the first input signal A, the second input terminal of the positive feedback XOR / XOR gate is used to access the second input signal B, The first input end of the output circuit is connected with the exclusive OR logic output end of the positive feedback exclusive OR / exclusive OR gate, the second input end...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More