Power semiconductor device and edge terminal region structure thereof, and processing method of edge terminal region structure

A power semiconductor and edge termination technology, applied in semiconductor devices, semiconductor/solid state device manufacturing, electric solid state devices, etc., can solve the problems of large edge termination area, unfavorable chip miniaturization, etc. The effect of miniaturization and improvement of withstand voltage capability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

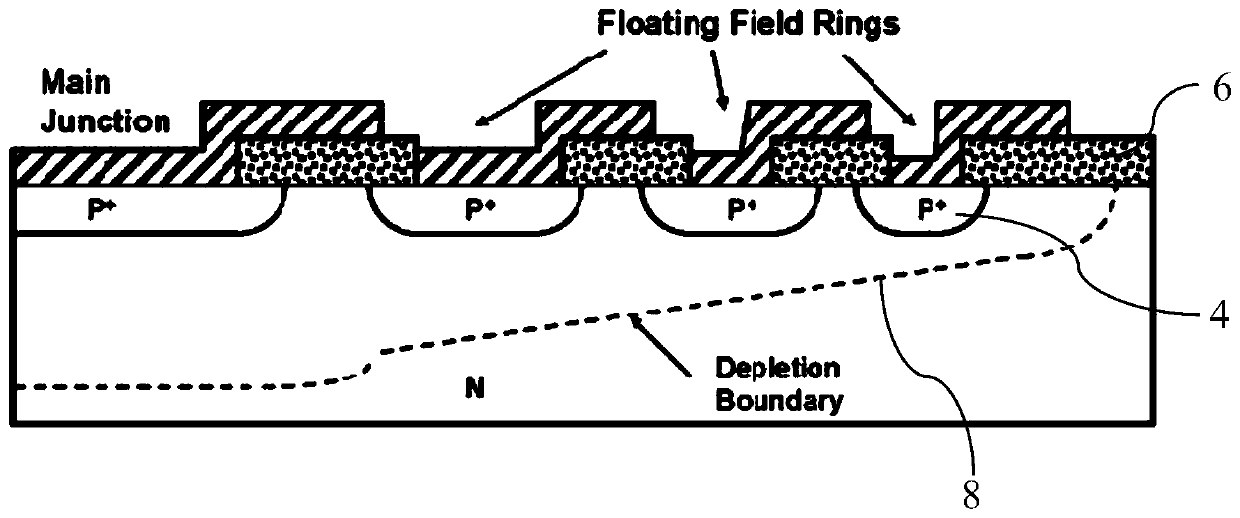

Problems solved by technology

Method used

Image

Examples

Embodiment

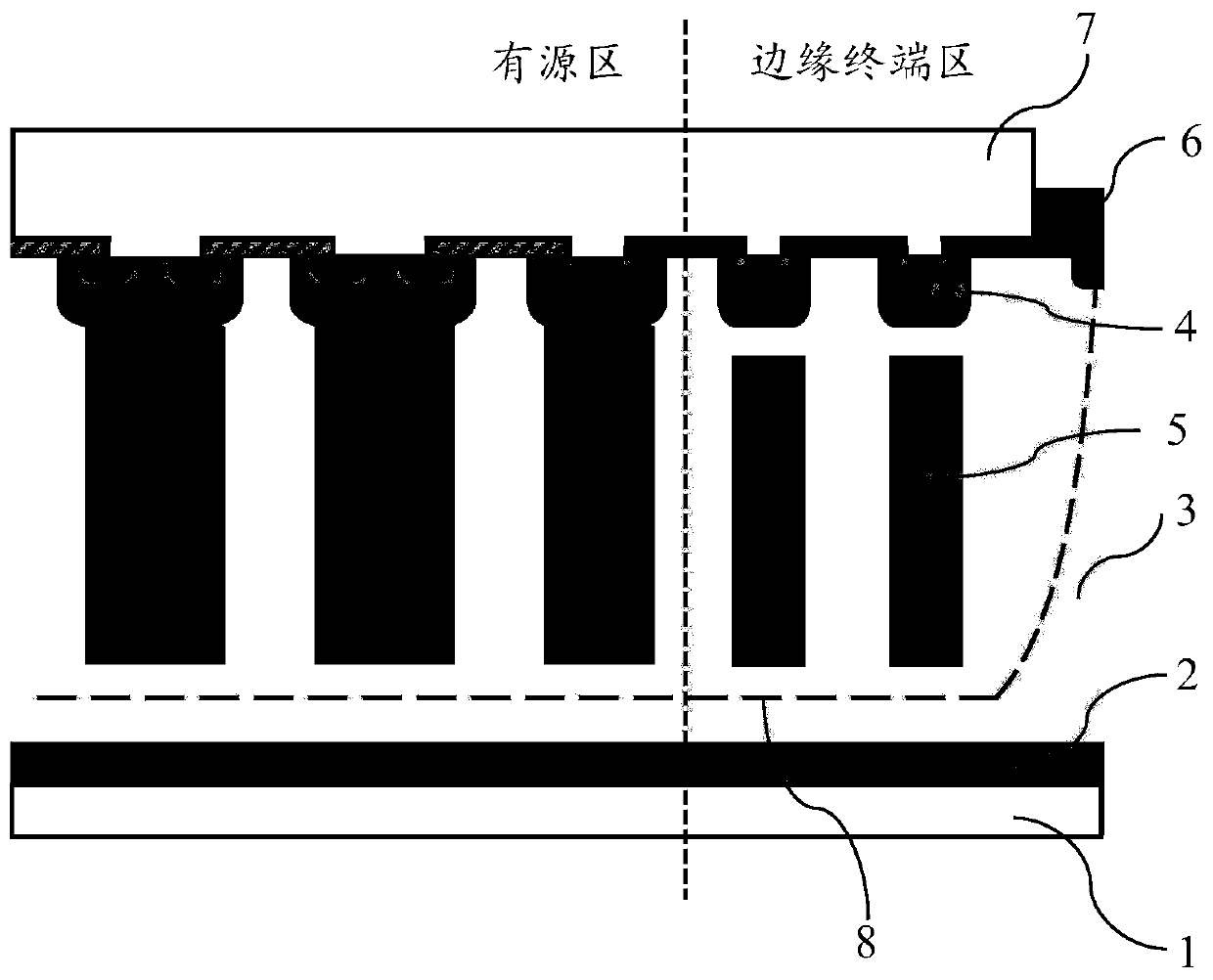

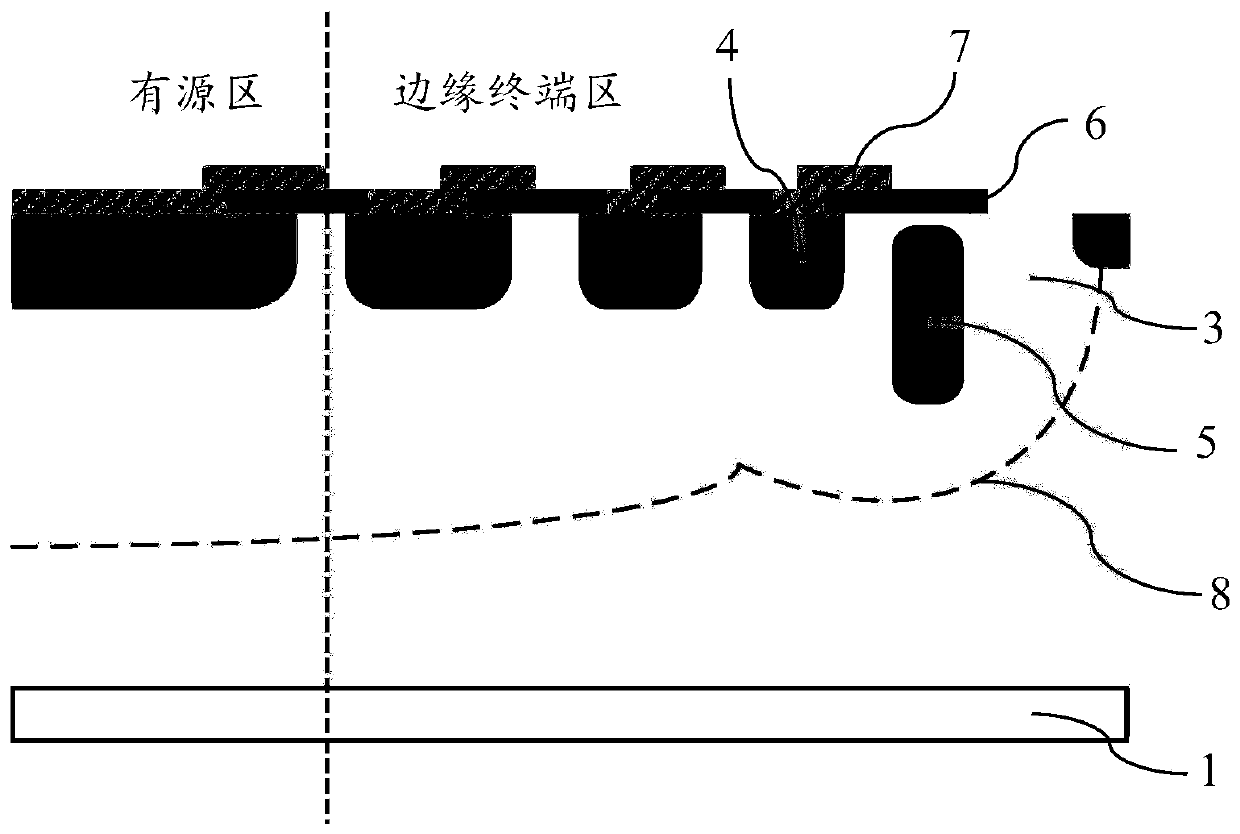

[0044] Such as figure 2 As shown, an embodiment of the present invention provides an edge termination region structure of a power semiconductor device, and the edge termination region includes:

[0045] (1) back metal electrode layer 1;

[0046] (2)N + a substrate 2 adjacent to the back metal electrode layer 1;

[0047] (3) N-type epitaxial layer 3, adjacent to the N + above the substrate 4;

[0048] (4) p-doped field ring 4, arranged on the upper surface of the N-type epitaxial layer 3;

[0049] (5) The floating p-layer ring 5 is arranged in the N-type epitaxial layer 3 and extends longitudinally in the N-type epitaxial layer 3 to extend the longitudinal depth of the space charge layer, and the boundary 8 of the space charge layer expands toward the back metal electrode layer 1 ;

[0050] (6) an insulating field plate 6, arranged above the p-doped field ring 4;

[0051] (7) The surface metal electrode layer 7 is disposed above the insulating field plate 6 and the p-do...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More