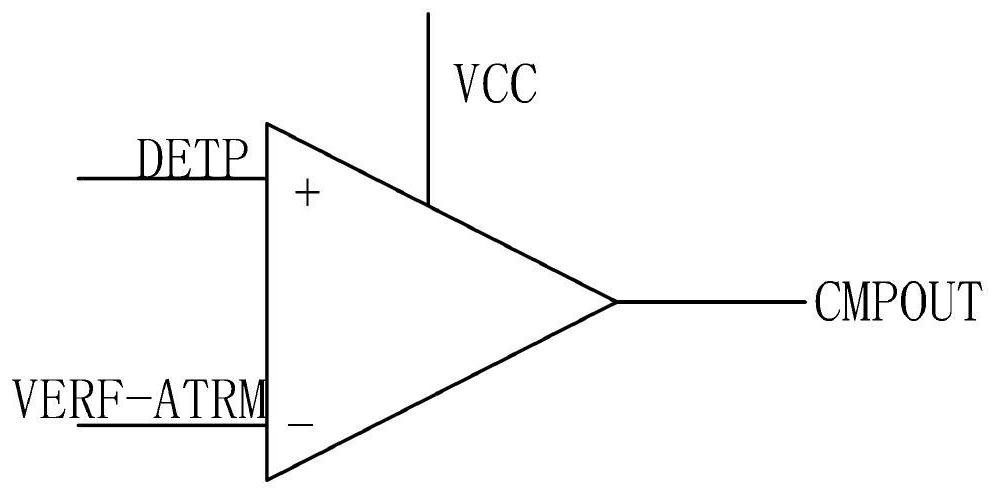

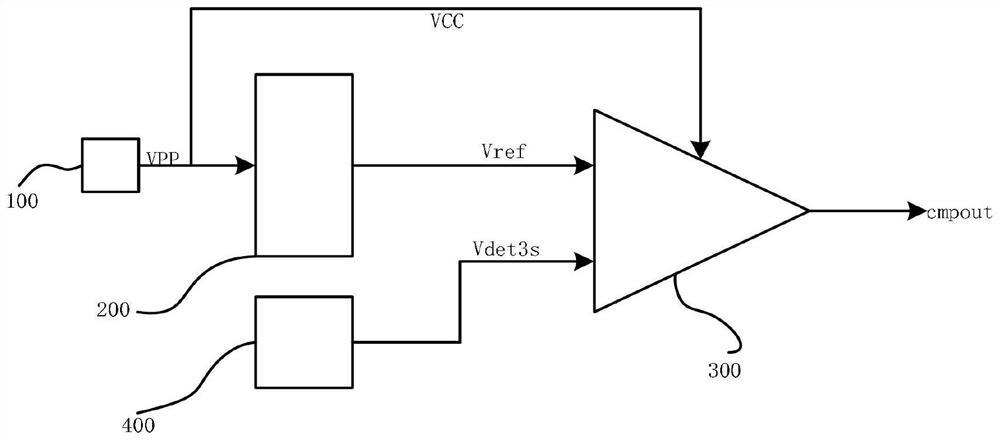

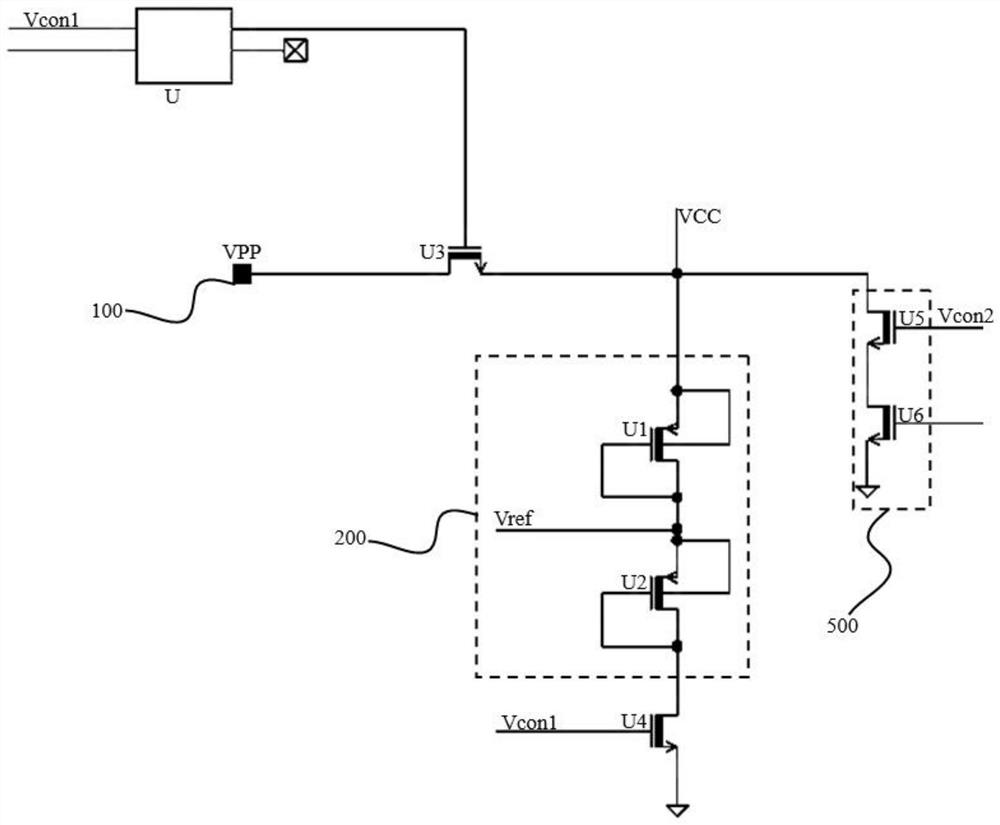

Erase voltage calibration circuit and data erase circuit of nonvolatile memory

A technology for erasing voltage and calibrating circuits, which is applied in static memory, read-only memory, information storage, etc., can solve problems such as poor calibration accuracy, and achieve the effects of improving calibration accuracy, reducing errors, and wide application range

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0049] The specific implementation manner of the present invention will be described in more detail below with reference to schematic diagrams. The advantages and features of the present invention will be more apparent from the following description. It should be noted that all the drawings are in a very simplified form and use imprecise scales, and are only used to facilitate and clearly assist the purpose of illustrating the embodiments of the present invention.

[0050] In the description of the present invention, it should be understood that the orientation or positional relationship indicated by the terms "center", "upper", "lower", "left", "right" etc. is based on the orientation or positional relationship shown in the drawings , is only for the convenience of describing the present invention and simplifying the description, but does not indicate or imply that the referred device or element must have a specific orientation, be constructed and operated in a specific orien...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More