Port configurable router design method based on wide-port heterogeneous tiles and router

A design method and router technology, applied in digital transmission systems, electrical components, transmission systems, etc., can solve the problems of reducing port bandwidth, low delay, and difficulty in meeting high-bandwidth and low-latency requirements, so as to alleviate pin bandwidth and hardware costs Realize and reduce the effect of chip area and wiring

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific implementation examples.

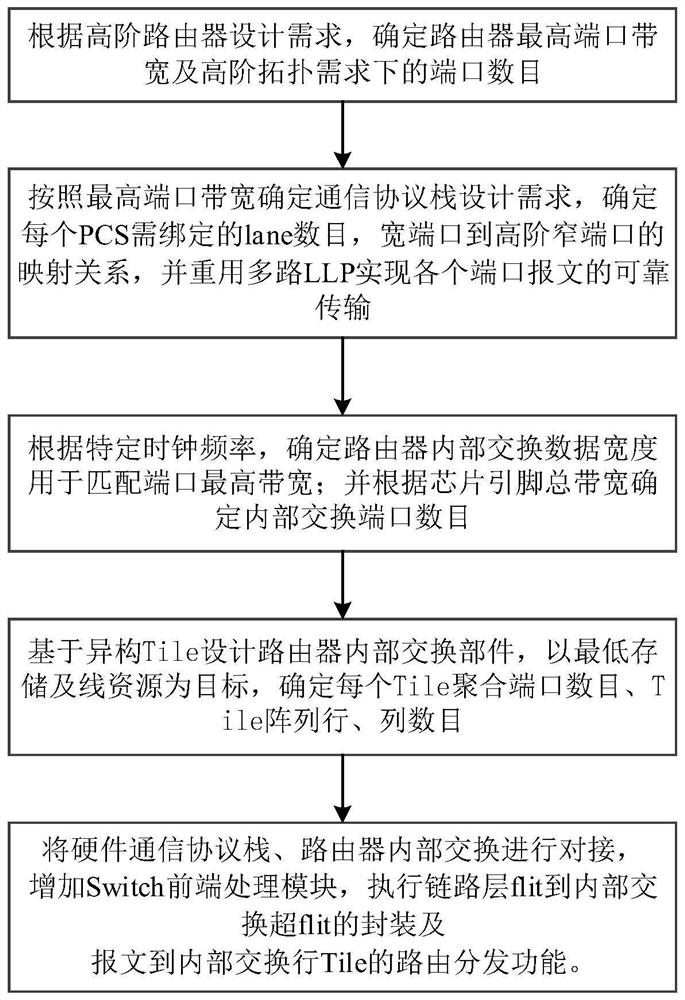

[0027] like figure 1 As shown, the implementation steps of the port-configurable router design method based on wide-port heterogeneous tiles in this embodiment include:

[0028] 1) Determine the maximum port bandwidth of the router and the number of ports required by the high-order topology;

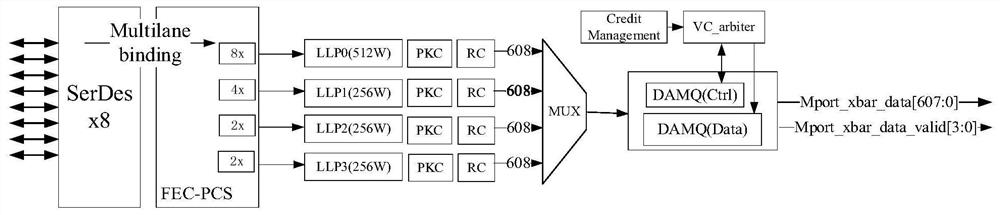

[0029] 2) Design the hardware communication protocol stack according to the highest port bandwidth, determine the number of lanes initially bound to each physical coding sublayer module, and the mapping relationship between wide ports and high-order narrow ports, and reuse multiple LLP (link layer) to realize each Reliable transmission of port messages;

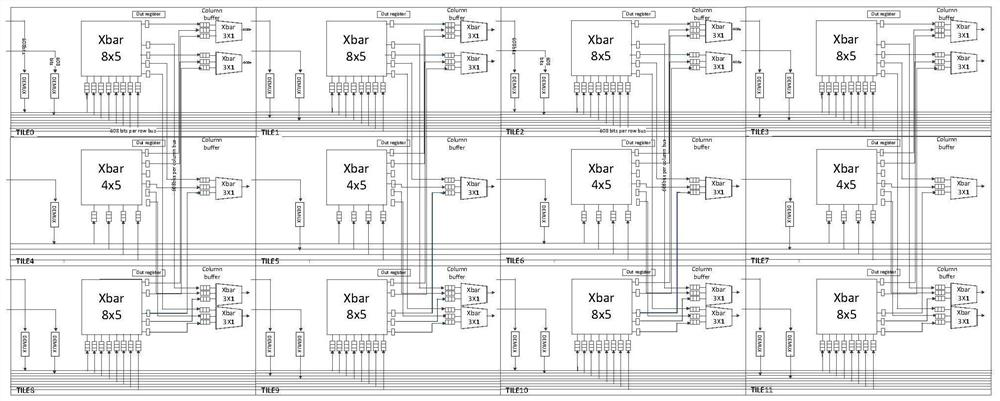

[0030]3) According to the specified clock frequency, determine the router's internal exchange data width to match the highest port bandwidth; and determine the number of internal ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More