Chip internal structure analysis method and sample bearing device

A technology of a sample carrying device and an analysis method is applied in the field of an internal structure analysis method of a chip and a sample carrying device, and can solve the problems of low accuracy of quantitative analysis and high difficulty in sample preparation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

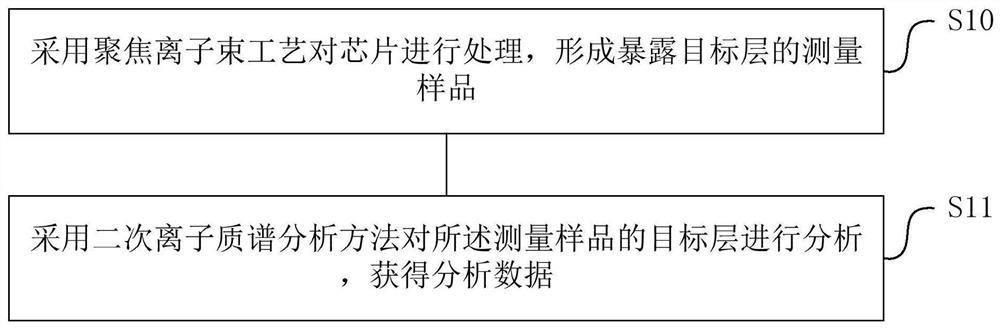

[0029] The specific implementations of the method for analyzing the internal structure of the chip and the sample carrying device provided by the present invention will be described in detail below in conjunction with the accompanying drawings.

[0030] As mentioned in the background art, the existing methods for analyzing the internal structure of chips have the problems of low quantitative analysis accuracy and high difficulty in sample preparation. Existing measurement and analysis methods include:

[0031] The disadvantage of using a test instrument with low resolution for measurement is that the accuracy of quantitative measurement is not high. The inventors found that the reason for the low accuracy is that when measuring an element with a low doping concentration, other elements as noise will affect the determination of the content of the element, thereby affecting the measurement accuracy of the element.

[0032] The disadvantage of measuring with a high-resolution te...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More