A fpga implementation method of lfmcw radar mtd processing

An implementation method, radar technology, applied in the input/output process of data processing, electrical digital data processing, program control, etc., can solve problems such as ease of use, limited storage resources, and inability to cache echo data, etc., to improve flexibility, Improve reliability and save hardware resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] The present invention will be described in further detail below with reference to the accompanying drawings and specific embodiments.

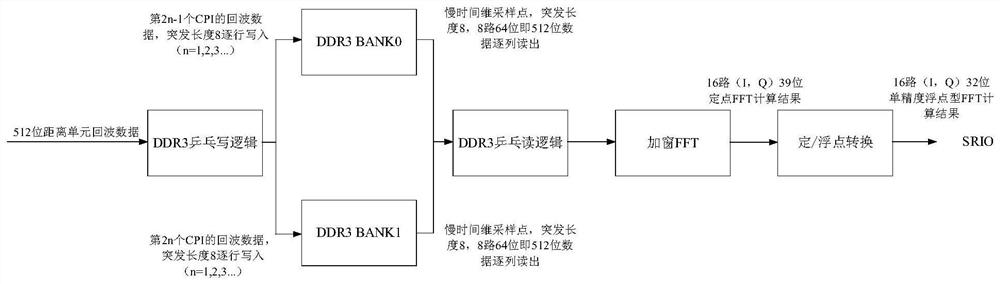

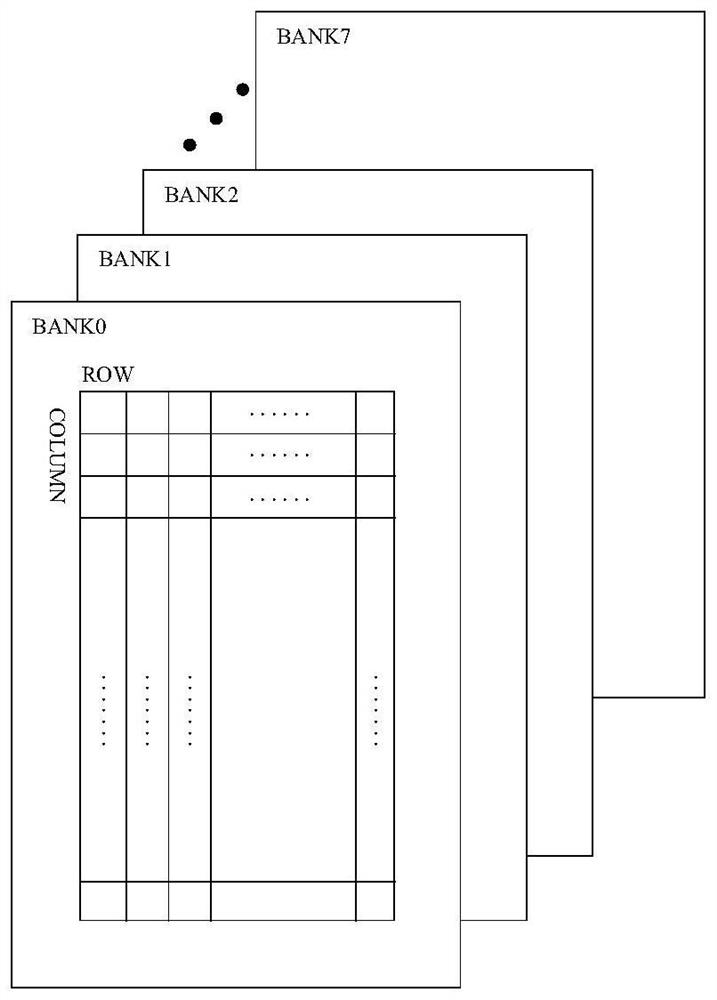

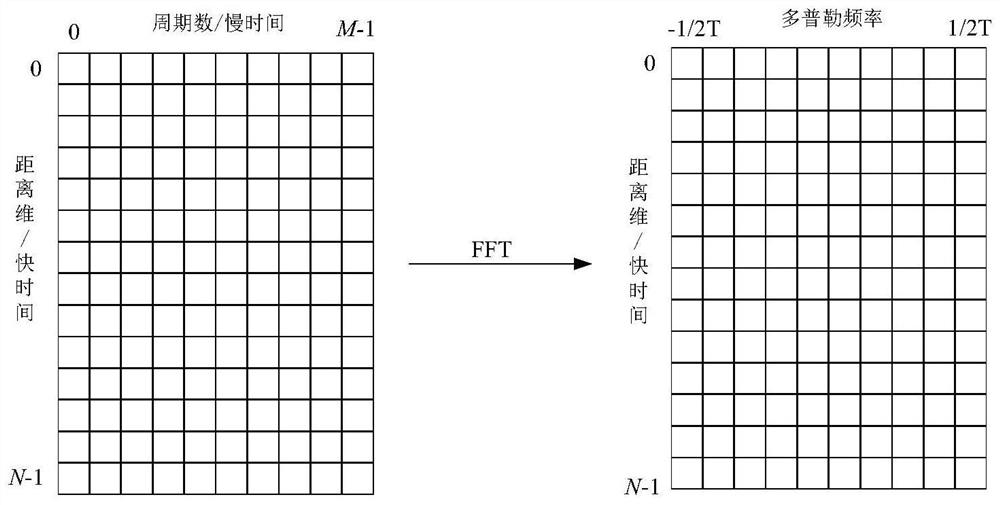

[0034]The method proposed by the present invention utilizes DDR3 SDRAM to cache radar echo data, performs address division and segmental read and write on it through FPGA to realize fast / slow time dimension conversion of echo data, and utilizes FFT IP core to realize slow time dimension data conversion. Finally, the fixed-point calculation results are converted into single-precision floating-point numbers to ensure the dynamic range and accuracy of the calculation results. The ModelSim simulation and hardware test in this paper are based on the FPGA device XC7V585T-2FFG1761I of the Xilinx V7 series, and the development platform is Vivado2019.2; 64-bit memory with a total capacity of 2GB. But this method also works for other Xilinx FPGA devices that support the DDR3 interface.

[0035] The steps of the present invention are as follows:...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More