FPGA-based design method for improving the speed of BCPNN

A design method and speed technology, applied in the field of artificial intelligence, can solve problems such as high computational complexity, achieve the effects of reducing resource consumption, increasing weight and bias update speed, and improving computing speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] It should be clear that the described embodiments are only some of the embodiments of the present invention, not all of them. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without creative efforts fall within the protection scope of the present invention.

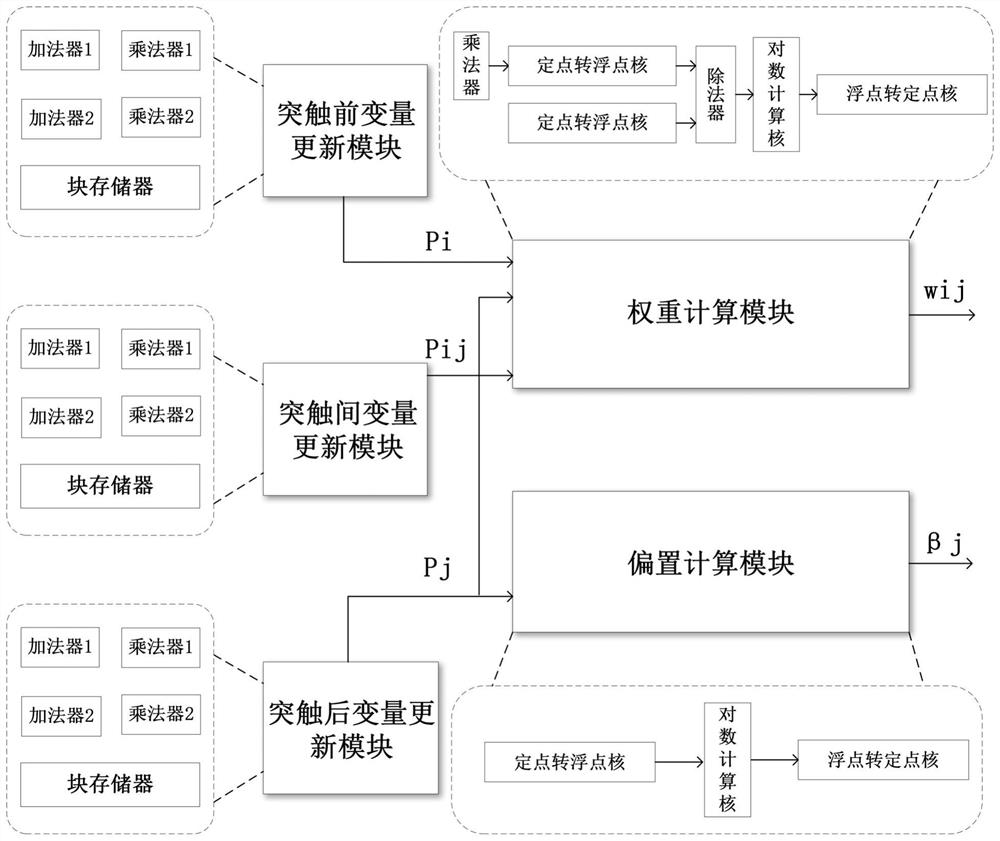

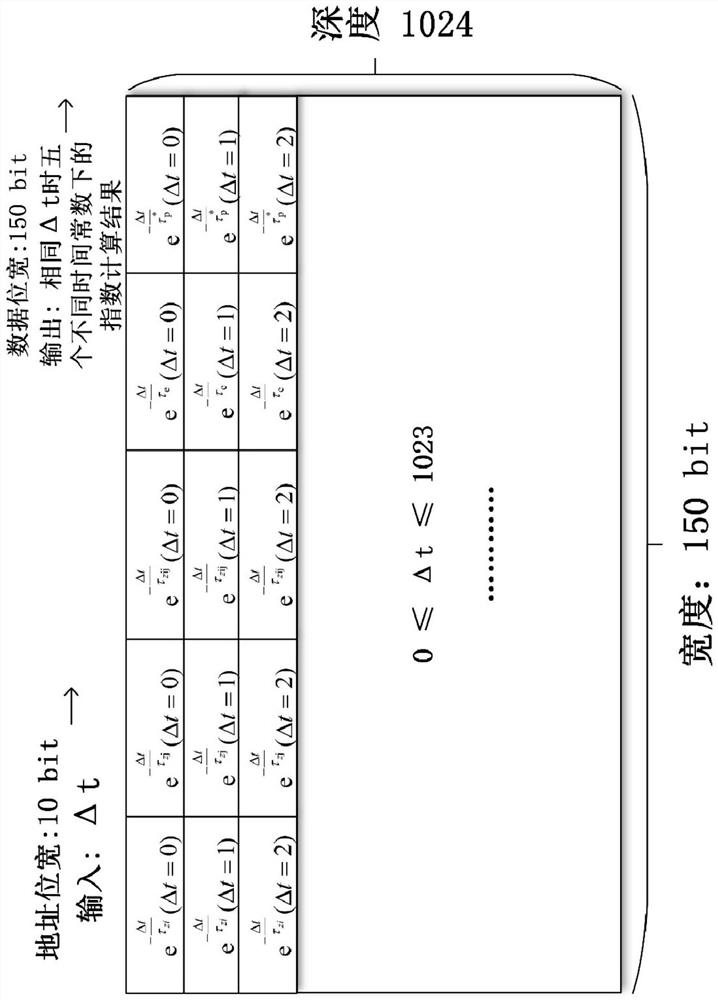

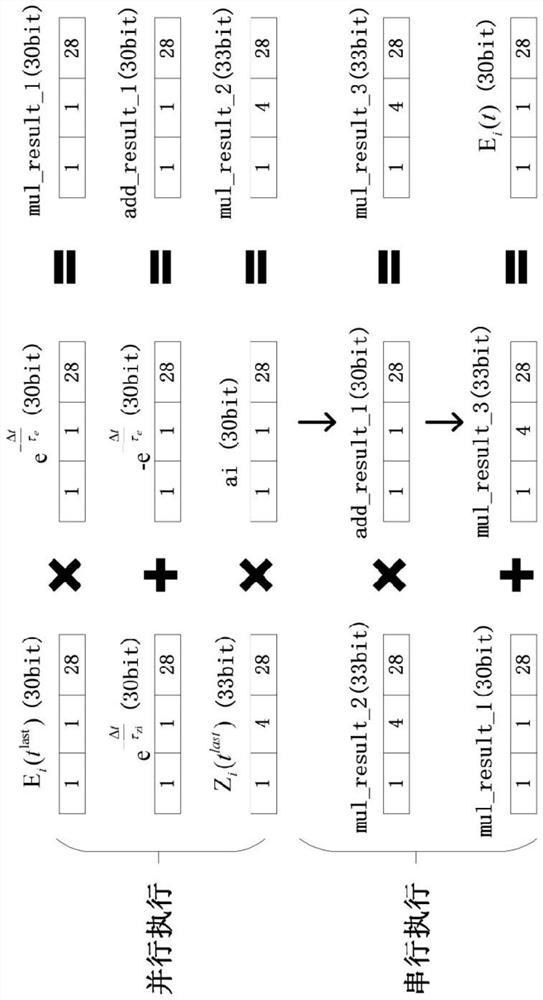

[0025] The present invention uses the method of modular design, and the goal is to accelerate the update process of the state variable, weight and bias of the Bayesian belief propagation neural network on the FPGA hardware, so as to obtain the purpose of improving the weight and bias update speed of the neural network . Among them, FPGA (Field Programmable Gate Array) is a product further developed on the basis of programmable devices such as PAL and GAL. It emerged as a semi-custom circuit in the field of application-specific integrated circuits (ASIC), which not only solves the shortcomings of custom circuits, but also overcomes the shortc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More