In-loop dual backup system

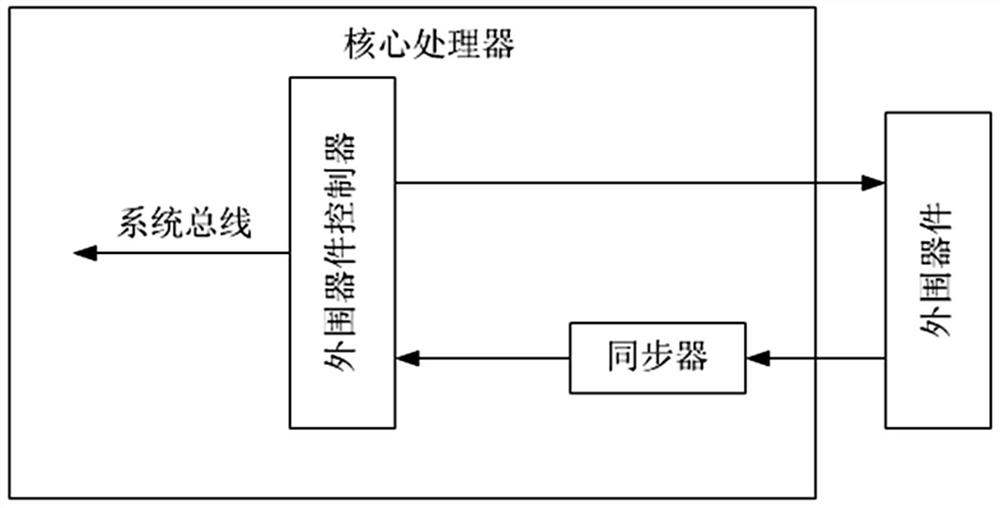

A dual backup and system bus technology, applied in the field of integrated circuits, can solve the problems of lower core processor performance and high complexity, and achieve the effect of reducing the risk of common cause failure and improving the fault diagnosis rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

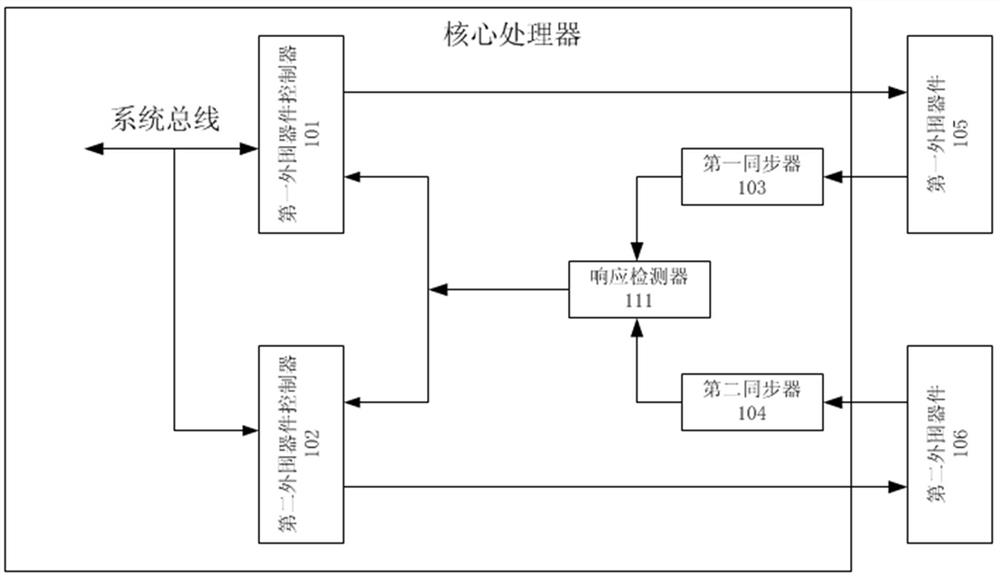

[0034] figure 2 It is a schematic structural diagram of an in-ring dual backup system according to Embodiment 1 of the present invention, as figure 2 As shown, the in-ring dual backup system of the present invention includes a first peripheral device controller 101, a second peripheral device controller 102, a first synchronizer 103, a second synchronizer 104, a first peripheral device 105, a second peripheral device 106, and response detector 111, where,

[0035] The first peripheral device controller 101, which receives the operation command to the first peripheral device 105 from the system bus, and parses the operation command into a control signal and sends it to the first peripheral device 105; receives the first peripheral device from the response detector 111 105 is the response result of execution according to the instruction of the control signal.

[0036] The second peripheral device controller 102, which delays the received operation command to the first periph...

Embodiment 2

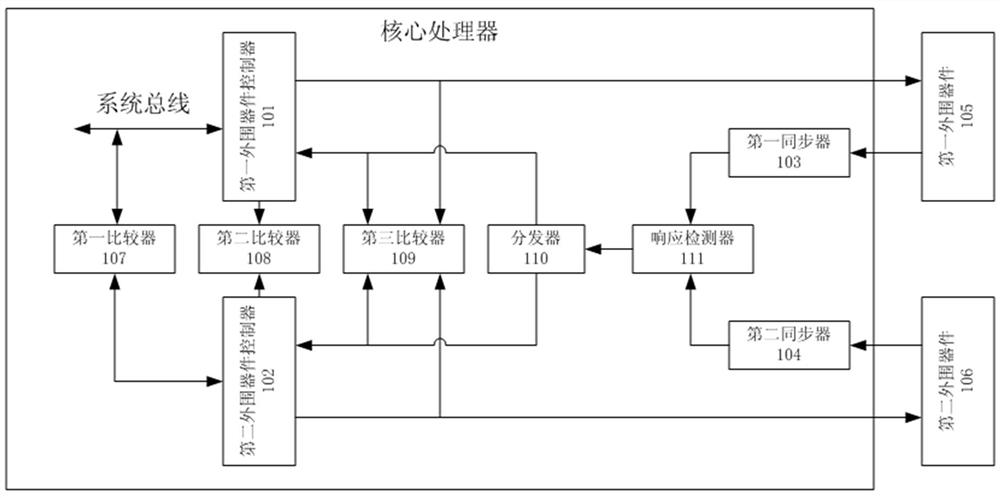

[0044] image 3 It is a schematic structural diagram of an in-ring dual backup system according to Embodiment 2 of the present invention, as shown in image 3 As shown, the in-ring dual backup system of the present invention includes a first peripheral device controller 101, a second peripheral device controller 102, a first synchronizer 103, a second synchronizer 104, a first peripheral device 105, a second Peripheral device 106, first comparator 107, second comparator 108, third comparator 109, distributor 110, and response detector 111, wherein,

[0045]The first peripheral device controller 101, which receives the operation command to the first peripheral device 105 from the system bus, and resolves the operation command as a control signal and sends it to the first peripheral device 105 and the third comparator 109; from the distributor 110 A response result of execution according to the instruction of the control signal of the first peripheral device 105 is received.

...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More