Wafer assembly with alignment marks, method for forming same, and method for aligning wafers

A technology for aligning marks and aligning marks, applied in the direction of electrical components, semiconductor devices, electric solid devices, etc., to achieve the effects of improving pattern clarity, solving bonding gaps, and improving bonding accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

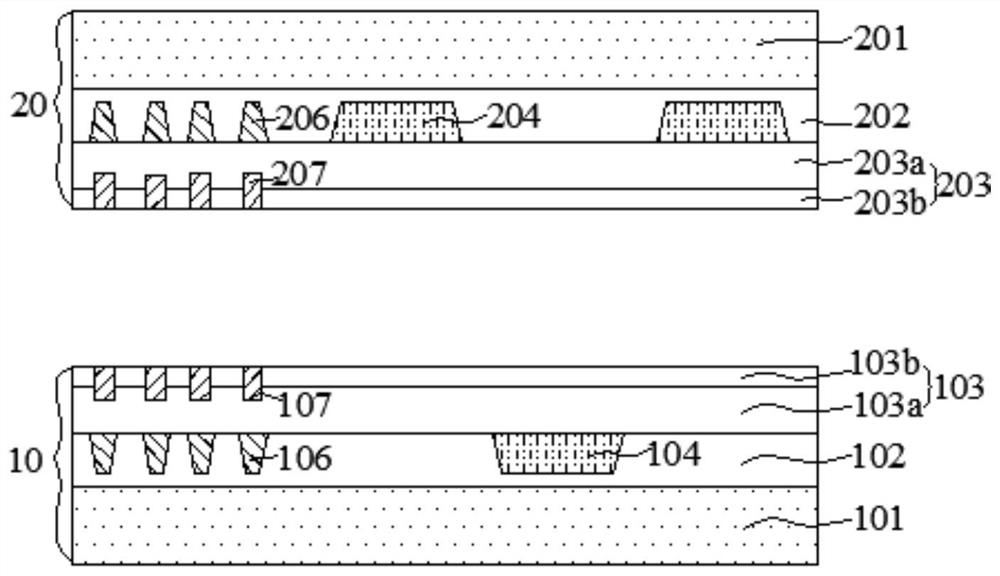

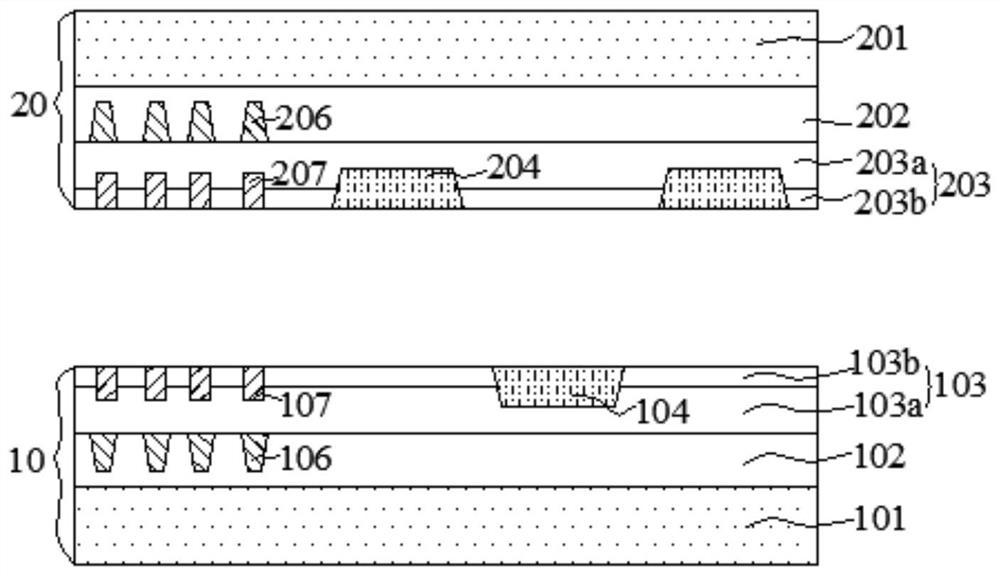

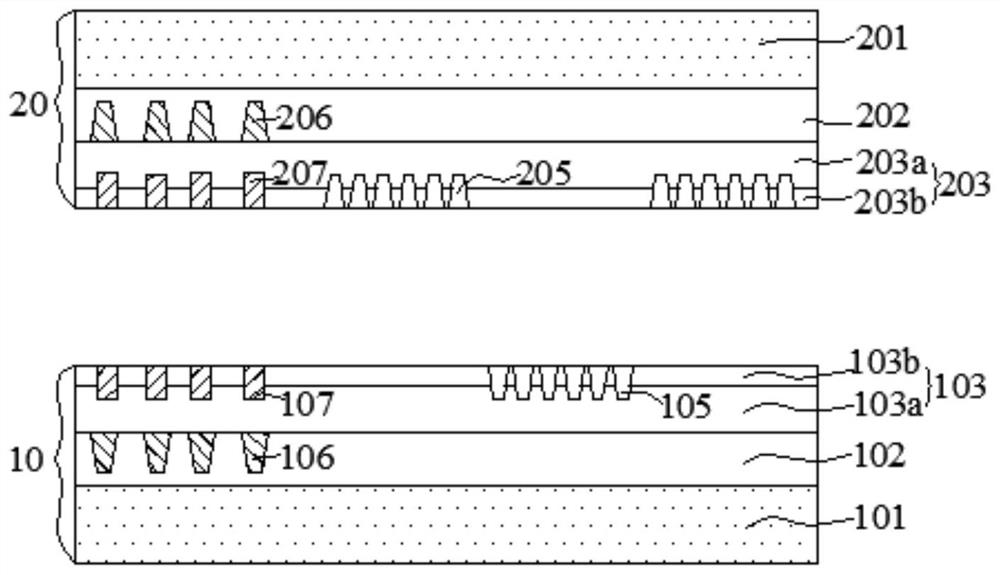

[0049] Embodiments of the present invention provide a wafer assembly with an alignment mark, a forming method thereof, and a wafer alignment method. The present invention will be described in further detail below in conjunction with the accompanying drawings and specific embodiments. The advantages and features of the present invention will become clearer from the following description. It should be noted that the drawings are all in a very simplified form and use imprecise scales, and are only used to facilitate and clearly assist the purpose of illustrating the embodiments of the present invention.

[0050] An embodiment of the present invention provides a wafer assembly with an alignment mark, including:

[0051] The first wafer, the first wafer includes a first substrate, a first dielectric layer on the first substrate, a first block mark embedded in the first dielectric layer, and a first block mark on the first substrate. The first bonding layer on the first dielectric...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com