FPGA on-orbit debugging method for component flight verification

A component and debugging information technology, applied in the direction of electrical components, radio transmission systems, transmission systems, etc., can solve the problem of unable to collect internal dynamic information of on-orbit FPGA, unable to realize on-orbit FPGA positioning and resolution, and unable to perform remote debugging tests, etc. To achieve the effect of solving the inability to collect internal dynamic information, broaden detection methods, and improve on-orbit life

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0033] Debugging methods include

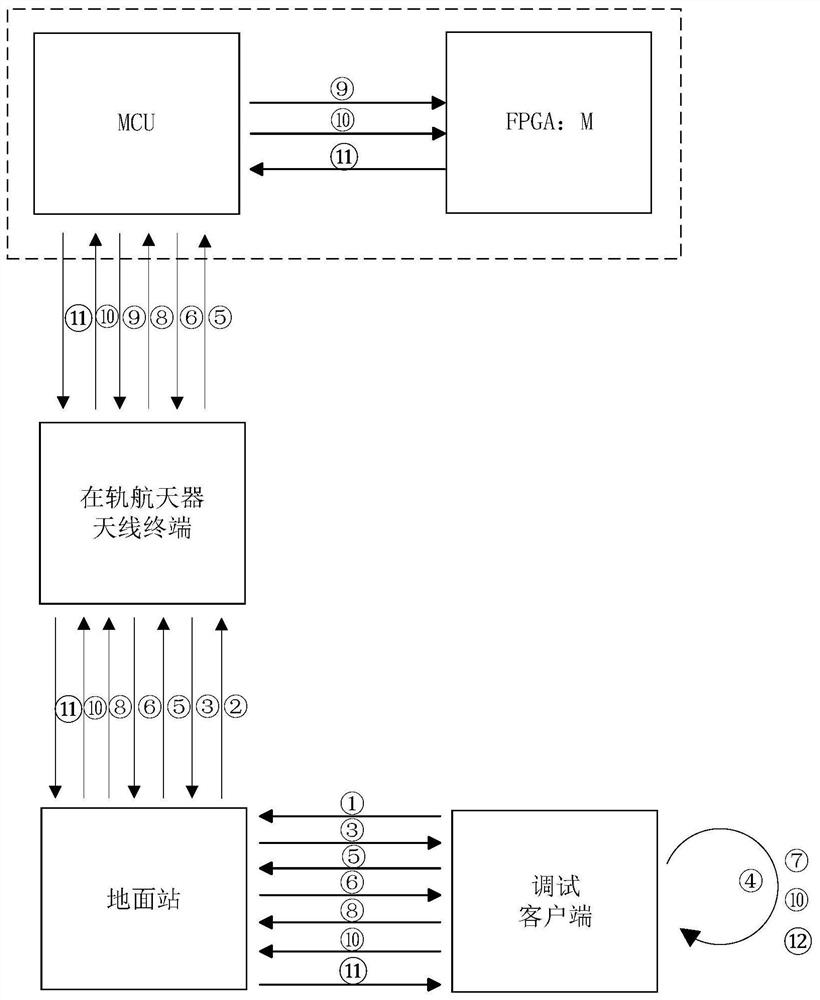

[0034] S1: The debugging client is connected to the ground station through a cable, and the ground station initiates a transmission request to the antenna terminal of the on-orbit spacecraft through the satellite-ground communication link. After waiting for the communication to be established, the ground terminal initiates a FPGA download or debugging information transmission request;

[0035] S2: After receiving the request information, the antenna terminal of the in-orbit spacecraft transmits the connection establishment information to the MCU through Ethernet;

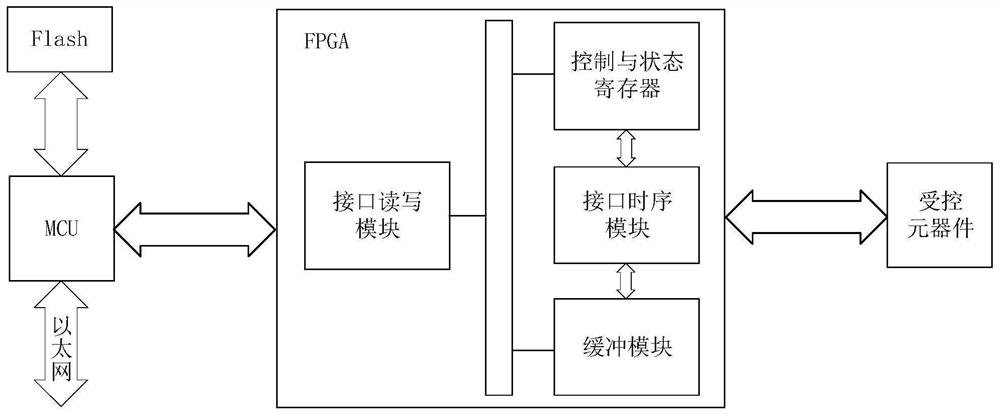

[0036] S3: MCU receives and parses the Ethernet data packet containing FPGA download or debugging information, and then sends the information to FPGA through a custom JTAG link;

[0037] S4: After the FPGA receives the download or debug information request information from the ground station, it returns the response response information and handshake data to the MCU;

[0038] S5: ...

Embodiment 2

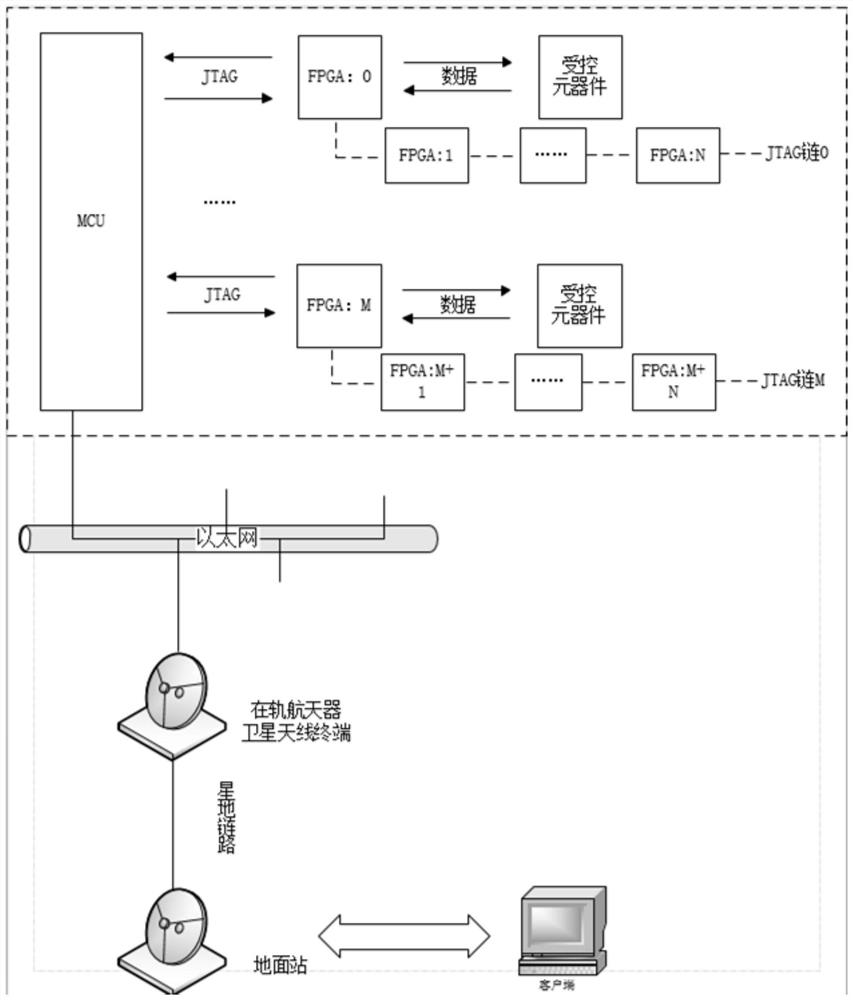

[0055] Preferably, in the steps S1, S2, S3, S4, S5, S6, S7, the method can realize the remote download and remote debugging of the FPGA on the track, and support the download of multiple FPGA devices of one or more JTAG chains and debugging;

[0056] Preferably, the connection established between the ground terminal and the FPGA under test in orbit includes "ground test terminal - ground communication terminal - antenna terminal on orbit spacecraft - control MCU on orbit - FPGA under test on orbit "The entire communication link, after research and testing, the delay of the link is within 100ms, which can meet the response time requirements of the ground debugging software.

[0057] Preferably, the remote FPGA debugging method is not only applicable to satellite-ground remote debugging, but also applicable to astronauts' in-orbit cabin debugging (such as debugging the external terminal FPGA in a space station) or ground equipment debugging tests.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More