Gate-controlled gallium oxide field effect transistor based on p-i-n structure and its preparation method

A field effect transistor, p-i-n technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as increasing device static power consumption, low device breakdown voltage, and reducing device reliability. Effects of static loss, improved breakdown voltage, and improved reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

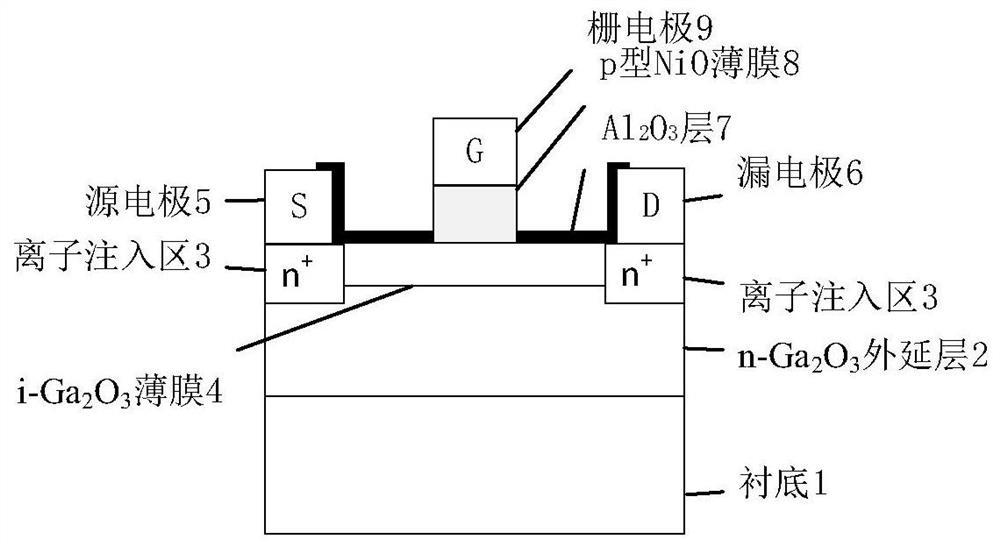

[0030] Embodiment 1, on the gallium oxide substrate of thickness 300nm, the thickness of making p-type NiO film on the n-type gallium oxide homoepitaxial wafer of thickness 200nm is 200nm, i-Ga 2 o 3 Gallium oxide transistors with a film thickness of 100nm.

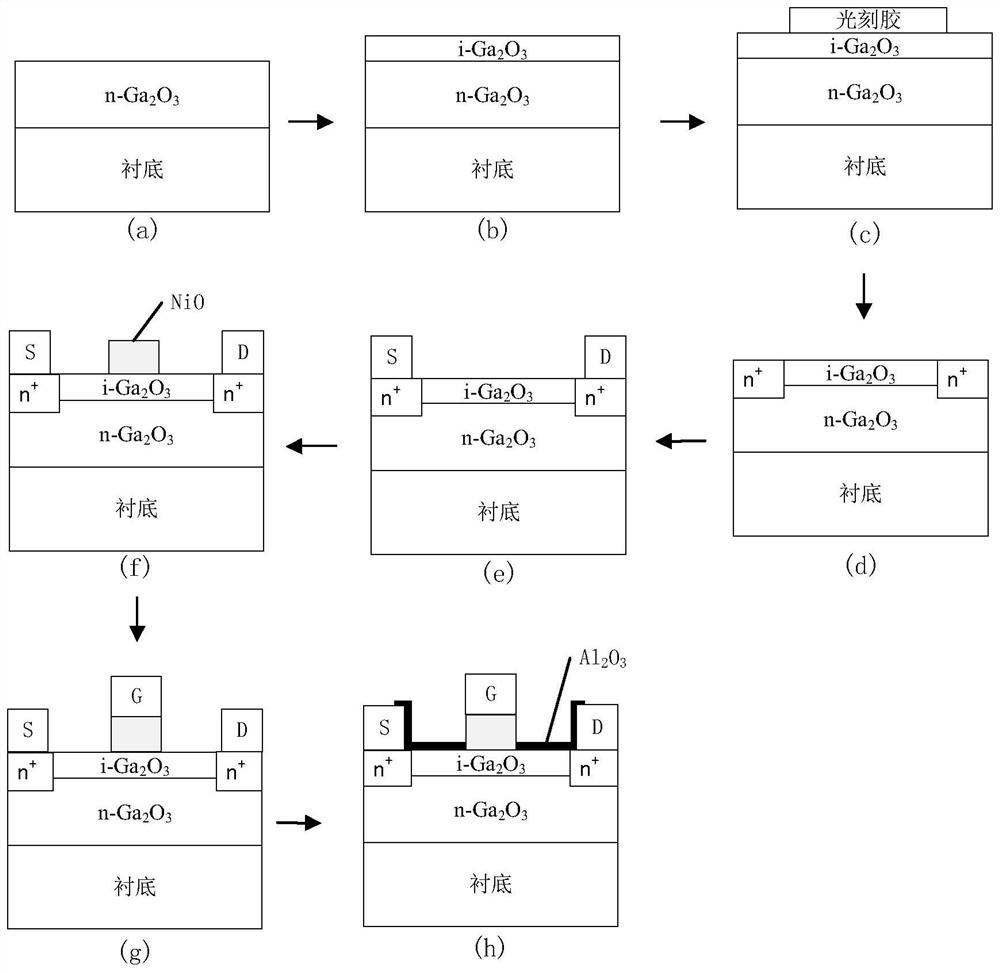

[0031] Step 1, cleaning the epitaxial wafer, such as image 3 (a).

[0032] Select the homoepitaxial gallium oxide epitaxial wafer and clean it, that is, place the homoepitaxial gallium oxide epitaxial wafer in acetone solution and absolute ethanol solution for 5 minutes, then rinse with a large amount of deionized water, and then blow it with nitrogen. Dry.

[0033] Step 2, Deposit i-Ga 2 o 3 film, such as image 3 (b).

[0034] Deposit i-Ga with a thickness of 100nm on the cleaned epitaxial wafer 2 o 3 The thin film layer is then annealed in an oxygen environment, the annealing temperature is 900°C, and the annealing time is 1h, so as to improve the interface contact performance.

[0035] Step 3, photolithogra...

Embodiment 2

[0047] Example 2, SiO with a thickness of 300nm 2 Insulating substrate, n-Ga with a thickness of 200nm 2 o 3 The thickness of the p-type NiO film made on the film is 300nm, i-Ga 2 o 3 Gallium oxide transistors with a film thickness of 120nm.

[0048] Step 1, cleaning the samples, such as image 3 (a).

[0049] 2.1) n-Ga with a thickness of 200nm 2 o 3 Thin films transferred to SiO with a thickness of 300 nm 2 on an insulating substrate;

[0050] 2.2) Put the transferred samples into acetone solution and anhydrous ethanol solution for 8 minutes for ultrasonic cleaning respectively, then rinse with a large amount of deionized water, and then blow dry with nitrogen.

[0051] Step 2, depositing i-Ga 2 o 3 film, such as image 3 (b).

[0052] n-Ga after cleaning 2 o 3 Deposit i-Ga with a thickness of 120nm on the film 2 o 3 The thin film layer is then annealed in an oxygen environment, the annealing temperature is 900°C, and the annealing time is 1h, so as to impro...

Embodiment 3

[0070] Embodiment 3, in the sapphire insulating substrate that thickness is 300nm, the n-Ga that thickness is 200nm 2 o 3 The thickness of the p-type NiO film made on the film is 200nm, i-Ga 2 o 3 Gallium oxide transistors with a film thickness of 80nm.

[0071] Step A, cleaning the sample, such as image 3 (a).

[0072] First, n-Ga with a thickness of 200nm 2 o 3 The thin film layer is transferred to a sapphire insulating substrate with a thickness of 300nm;

[0073] Then, the transferred samples were placed in acetone solution and absolute ethanol solution for 6 min, respectively, for ultrasonic cleaning, rinsed with a large amount of deionized water, and then dried with nitrogen.

[0074] Step B, Deposit i-Ga 2 o 3 film, such as image 3 (b).

[0075] n-Ga after cleaning 2 o 3 Deposit i-Ga with a thickness of 80nm on the film 2 o 3 The thin film layer is then annealed in an oxygen environment, the annealing temperature is 900°C, and the annealing time is 1h, ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More