VMAC high-speed address learning method and electronic equipment

A technology of address learning and V-UMAC, which is applied in the field of VMAC high-speed address learning method and electronic equipment, can solve the problem of limited update of VMAC address learning speed, achieve simple and fast refresh mechanism, improve data processing rate, and reduce data error handling Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0049] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention. In addition, the technical features involved in the various embodiments of the present invention described below can be combined with each other as long as they do not constitute a conflict with each other.

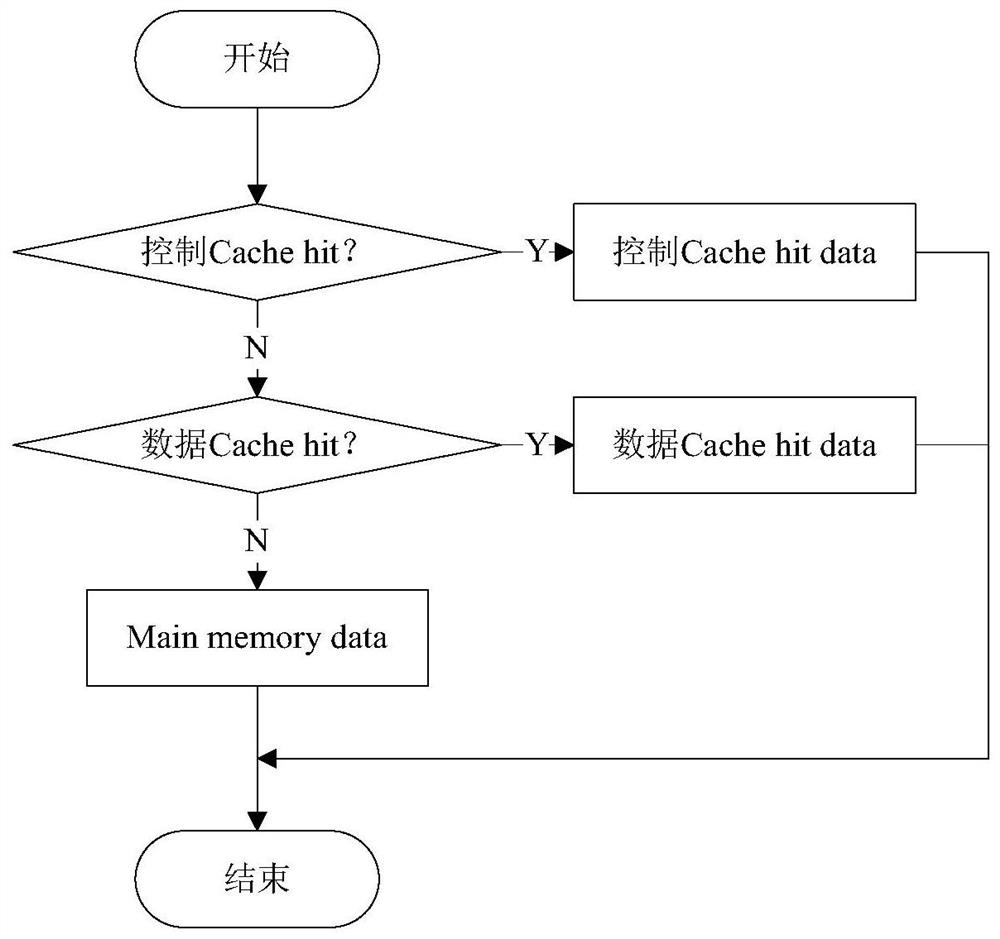

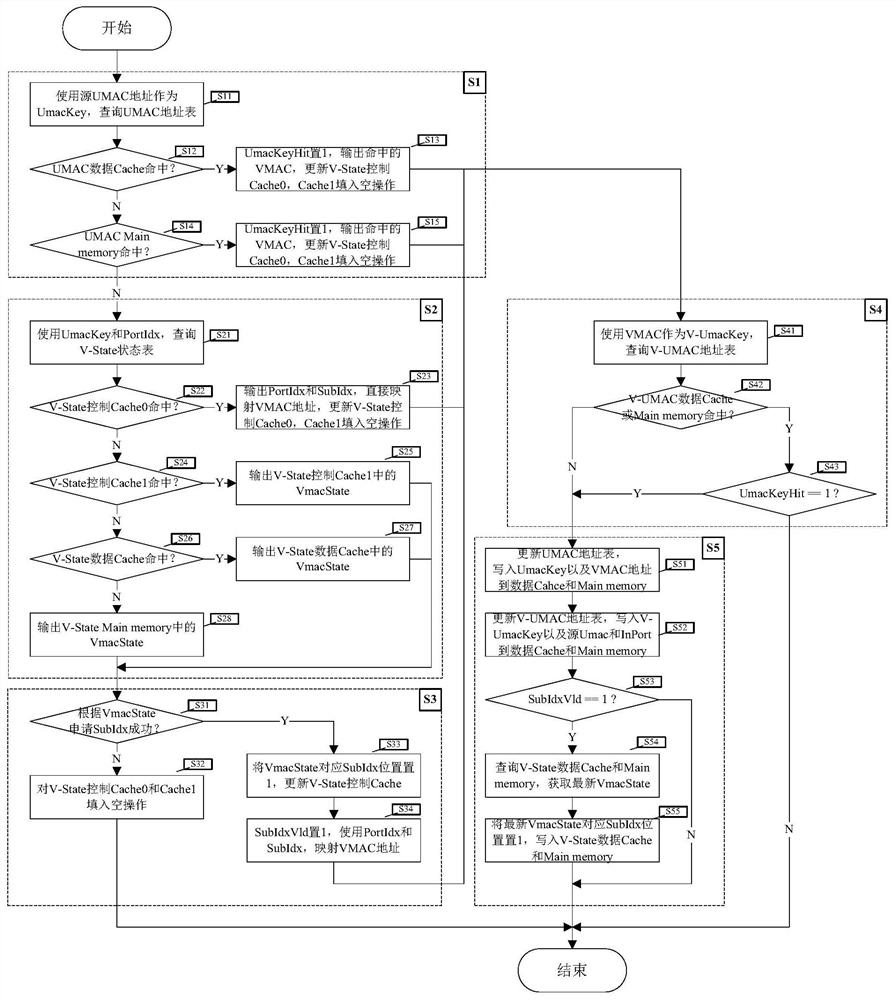

[0050] In order to improve the VMAC address learning speed and realize the high-speed pipeline processing of VMAC address learning, the present invention proposes a structure of "Control Cache", "Data Cache" and Main memory, and proposes a "Control Cache" refresh mechanism to reduce the high-speed processing data error processing rate.

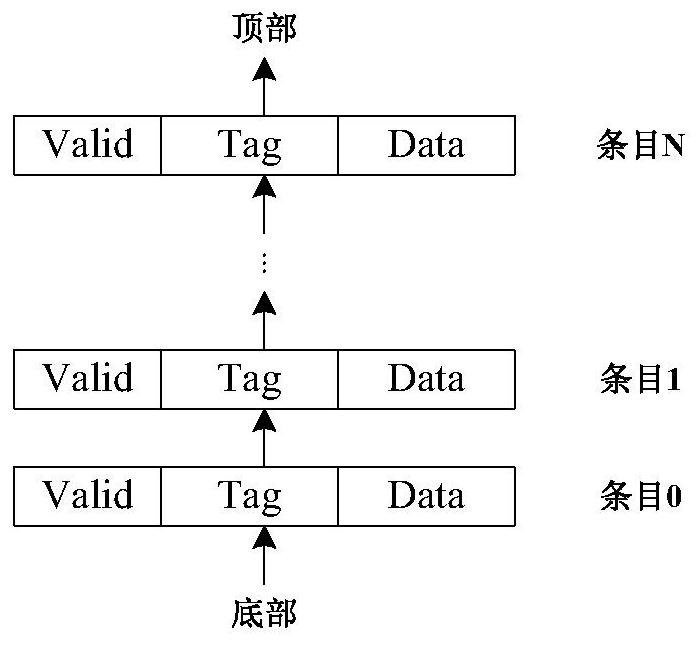

[0051] The structure of the Cache is a first-in-first-out...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More