Method and device for reducing network-on-chip power consumption, CPU chip and server

A CPU chip and network-on-chip technology, applied in the computer field, can solve problems such as the inability to adjust the NoC operating frequency accurately

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0067] The embodiments of the present invention will be described in detail below with reference to the accompanying drawings.

[0068] It should be understood that the described embodiments are only some, but not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by those of ordinary skill in the art without creative efforts shall fall within the protection scope of the present invention.

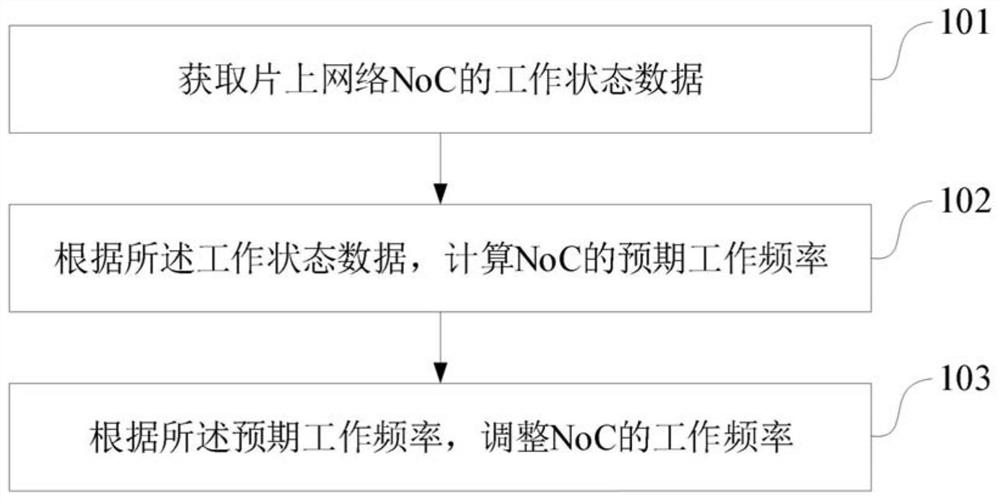

[0069] On the one hand, an embodiment of the present invention provides a method for reducing power consumption of an on-chip network, such as figure 2 As shown, the method of this embodiment may include:

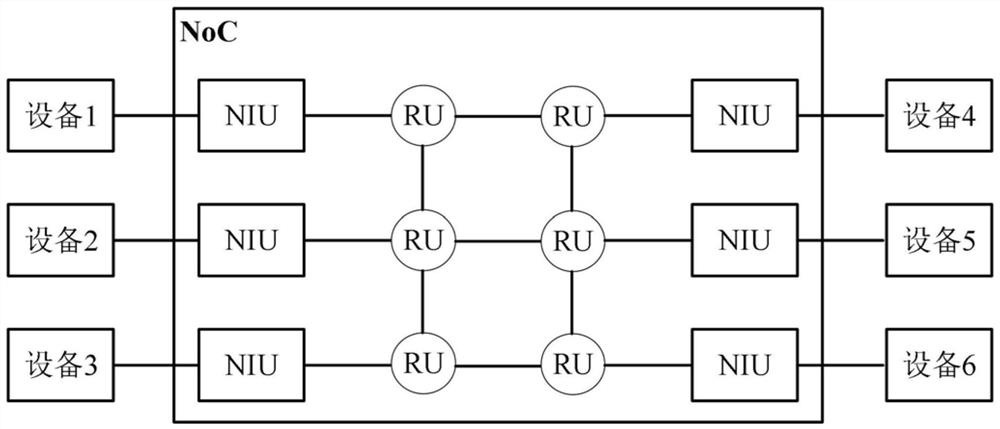

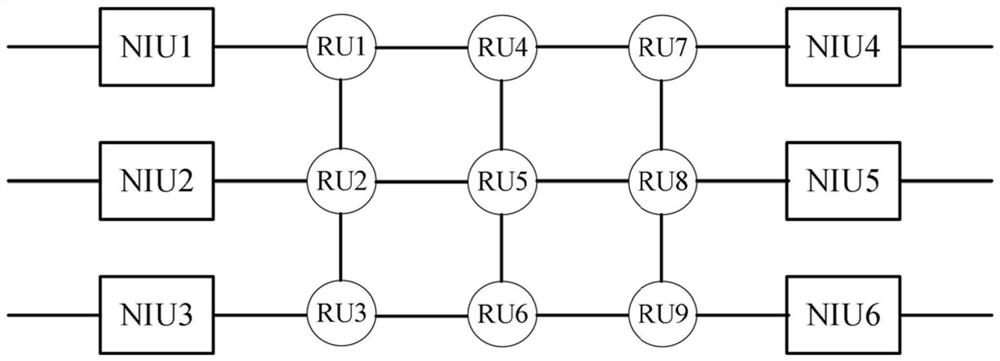

[0070] Step 101: Obtain the working status data of the network-on-chip NoC, the working status data includes the number of unresponsive requests initiated from the device in the NIU within a period of time window, the number of requests and responses cached in the RU within a period of time window, and the histo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More