Manufacturing method of PMOS

A manufacturing method and wafer technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of inability to dynamically adjust different silicon chips, and the inability to improve the performance uniformity of chip and chip devices, so as to improve the on-chip Uniformity, the effect of improving uniformity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

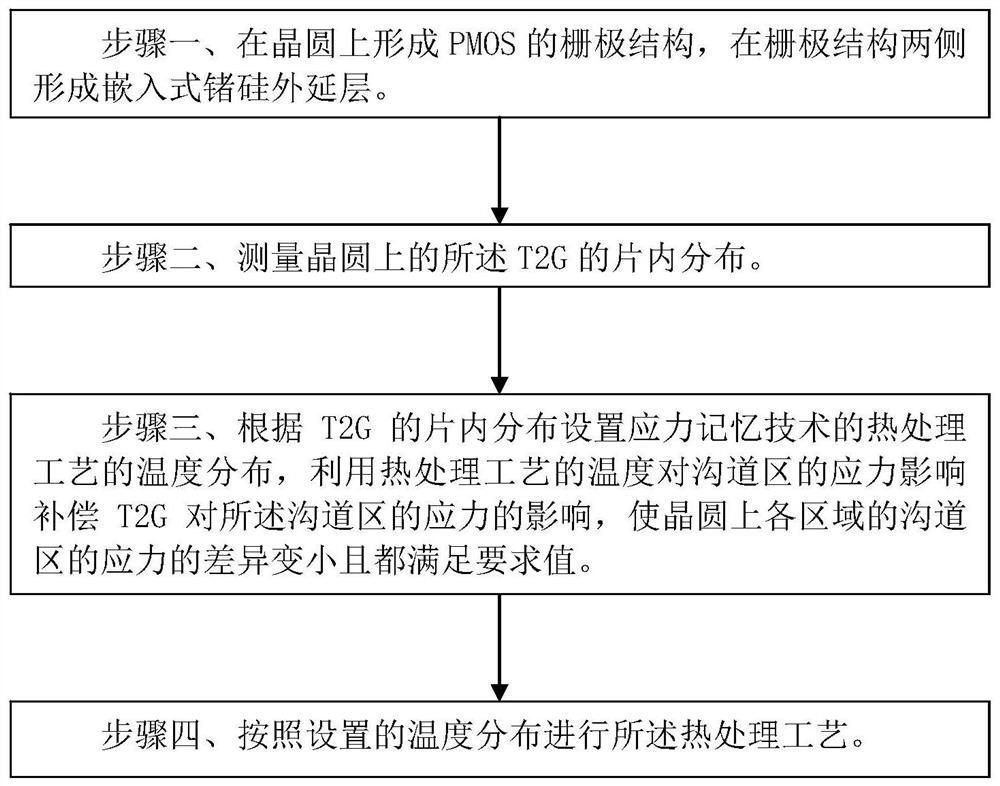

[0045] Such as figure 1 Shown is the flowchart of the manufacturing method of the PMOS embodiment of the present invention; the manufacturing method of the PMOS embodiment of the present invention includes the following steps:

[0046] Step 1. Form a PMOS gate structure on the wafer, and form an embedded silicon-germanium epitaxial layer on both sides of the gate structure. The embedded silicon-germanium epitaxial layer is formed in the groove, and T2G is the embedded silicon-germanium epitaxial layer. The distance between the tip of the silicon germanium epitaxial layer and the gate structure; the wafer is composed of a semiconductor substrate, and a plurality of the PMOSs are integrated on the wafer, and the semiconductor covered by the gate structure A channel region is formed on the surface of the substrate.

[0047] In the embodiment of the present invention, the gate structure is formed by stacking a gate dielectric layer and a polysilicon gate, and the forming steps of t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More