Chip reset method and system, storage medium and electronic equipment

A reset method and chip technology, applied in the computer field, can solve problems such as program hangs and abnormal operation of digital circuits.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

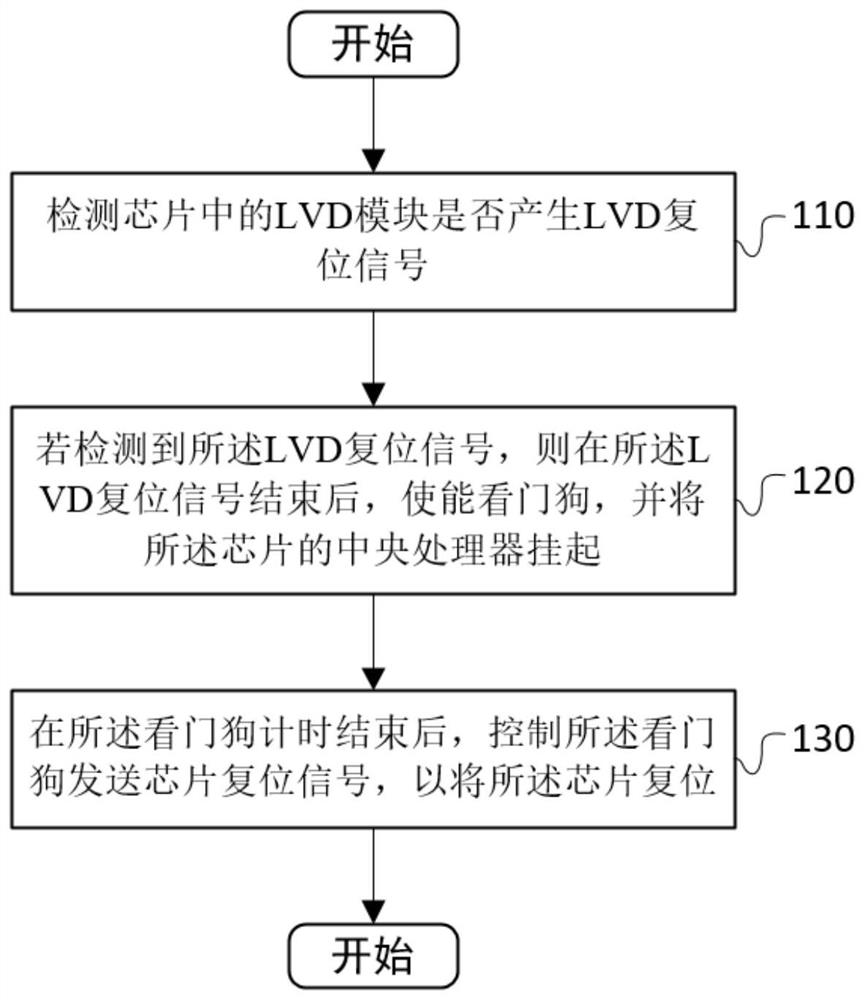

[0024] According to an embodiment of the present invention, a chip reset method is provided, figure 1 It shows a schematic flowchart of a chip reset method proposed in Embodiment 1 of the present invention, as shown in figure 1 As shown, the chip reset method may include: Step 110 to Step 130 .

[0025] In step 110, it is detected whether the LVD module in the chip generates an LVD reset signal.

[0026] Here, by detecting whether the LVD reset signal is detected, it can be judged whether the chip is faulty. The LVD module is a module used to detect the power supply voltage of the chip inside the chip. When the LVD module detects that the power supply voltage of the chip has dropped from the normal voltage to the set value, it will generate a reset signal to the chip to reset the chip. For example, the power supply voltage of the chip is 5V, and the voltage triggering the LVD reset signal is 4.1V, then the LVD module generates the LVD reset signal when the working voltage of...

Embodiment 2

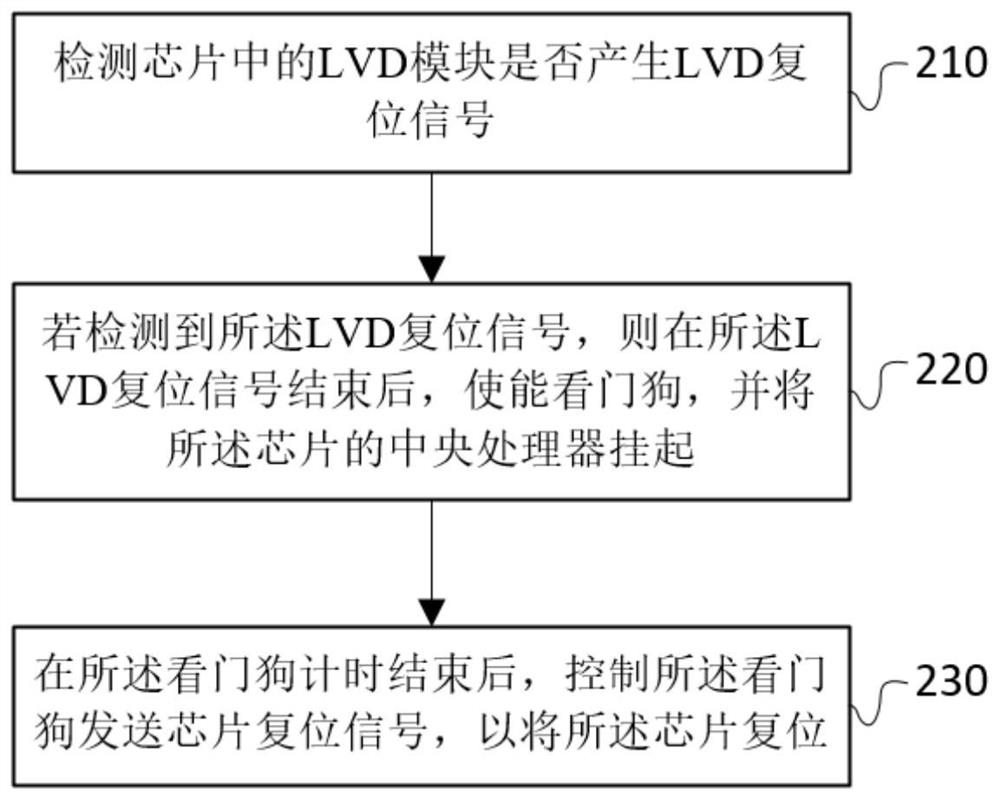

[0035] On the basis of the above embodiments, another embodiment of the present invention also provides a chip reset method, figure 2 It shows a schematic flowchart of a chip reset method proposed in Embodiment 2 of the present invention, as shown in figure 2 As shown, the chip reset method may include: Step 210 to Step 230 .

[0036] In step 210, it is detected whether the LVD module in the chip generates an LVD reset signal.

[0037] Here, by detecting whether the LVD reset signal is detected, it can be judged whether the chip is faulty. The LVD module is a module used to detect the power supply voltage of the chip inside the chip. When the LVD module detects that the power supply voltage of the chip has dropped from the normal voltage to the set value, it will generate a reset signal to the chip to reset the chip. For example, the power supply voltage of the chip is 5V, and the voltage triggering the LVD reset signal is 4.1V, then the LVD module generates the LVD reset ...

Embodiment 3

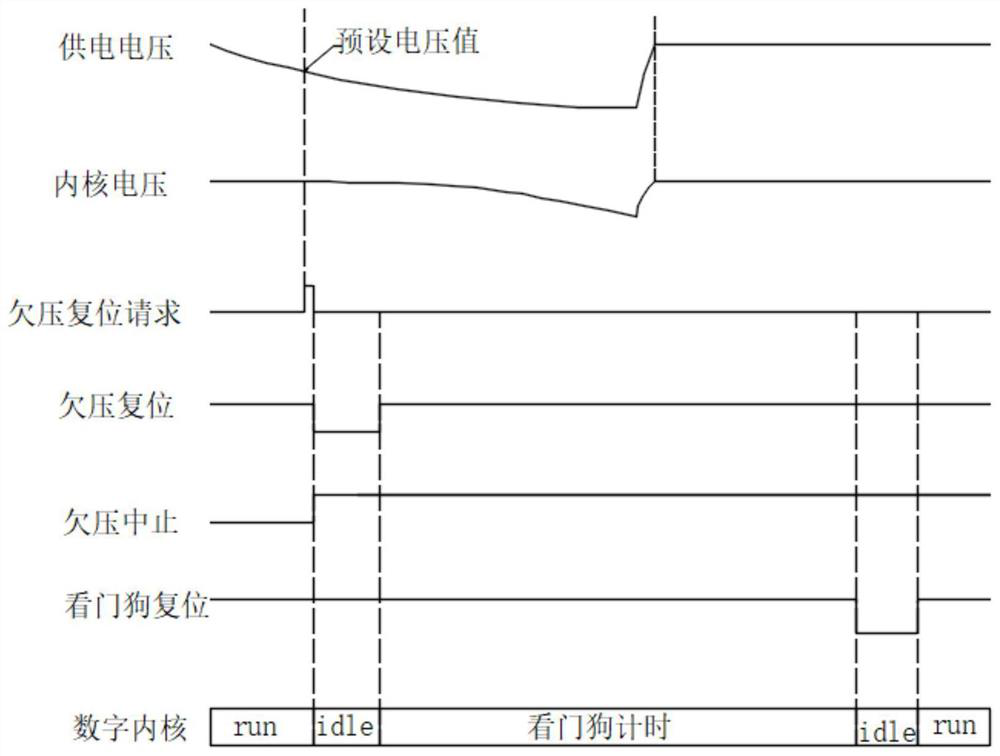

[0058] According to an embodiment of the present invention, a chip reset system corresponding to a chip reset method is also provided. see Figure 4 A schematic structural diagram of a chip reset system proposed by an embodiment of the present invention is shown. A chip reset system, comprising:

[0059] The detection module is used to detect the LVD reset signal generated by the LVD module in the chip;

[0060] A control module, configured to enable the watchdog and suspend the central processing unit of the chip after the LVD reset signal ends;

[0061] The control module is further configured to control the watchdog to send a chip reset signal to reset the chip after the watchdog timer ends.

[0062] Optionally, the timing time of the watchdog is not less than the time for the chip to fall from a preset voltage value capable of triggering the LVD reset signal to a completely power-down state.

[0063] Optionally, if the detection module does not detect the LVD reset sig...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More