Logic comprehensive control method and device

A logic synthesis and control method technology, applied in the FPGA field, can solve problems such as reducing development efficiency and increasing development time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

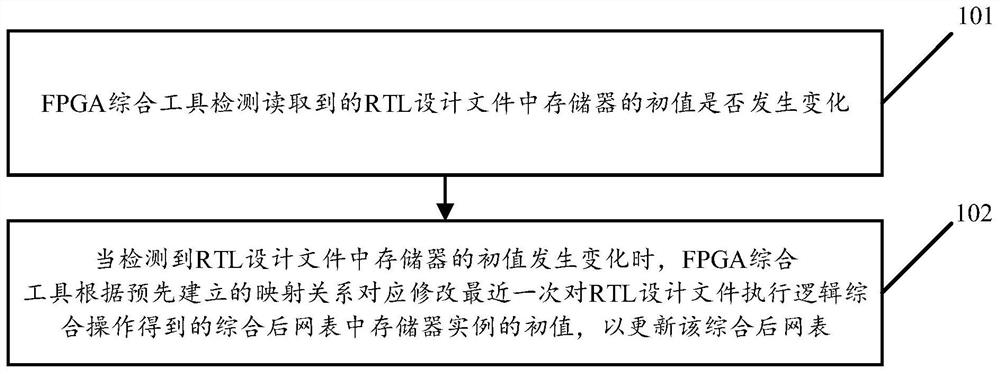

[0060] see figure 1 , figure 1 It is a schematic flowchart of a logic synthesis control method disclosed in an embodiment of the present invention. in, figure 1 The described method can be applied to an FPGA synthesis tool, and the FPGA synthesis tool can be combined with artificial intelligence to realize the application of FPGA in the field of artificial intelligence. Such as figure 1 As shown, the method may include the following operations:

[0061] 101. Whether the initial value of the memory in the read RTL design file detected by the FPGA synthesis tool changes; when the judgment result of step 101 is yes, trigger execution of step 102; when the judgment result of step 101 is no, this program can be ended The sub-process can also continue to trigger the execution of step 101.

[0062] In the embodiment of the present invention, in the development and design process of FPGA, the memory (memory) defined in the RTL design file will usually be inferred (infer) as the m...

Embodiment 2

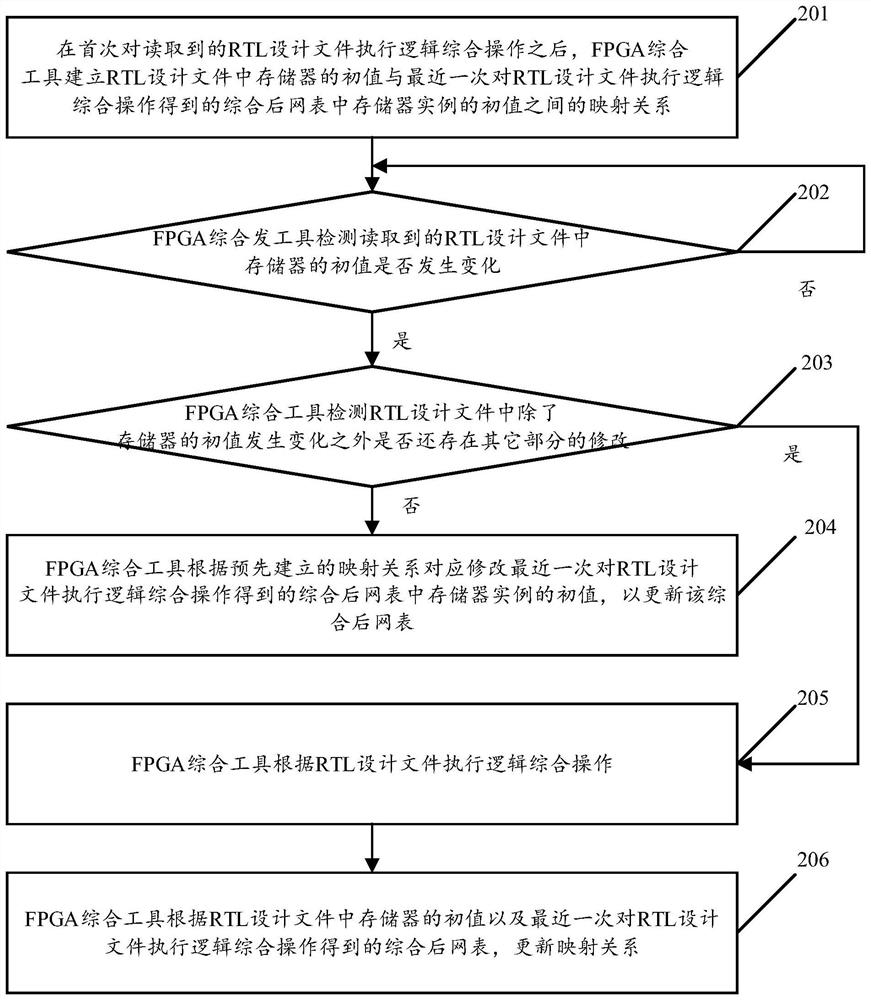

[0084] see figure 2 , figure 2 It is a schematic flowchart of another logic synthesis control method disclosed in the embodiment of the present invention. in, figure 2 The described method can be applied to an FPGA synthesis tool, and the FPGA synthesis tool can be combined with artificial intelligence to realize the application of FPGA in the field of artificial intelligence. Such as figure 2 As shown, the method may include the following operations:

[0085] 201. After the logic synthesis operation is performed on the read RTL design file for the first time, the FPGA synthesis tool establishes the initial value of the memory in the RTL design file and the memory instance in the post-synthesis netlist obtained by performing the logic synthesis operation on the RTL design file last time The mapping relationship between the initial values of .

[0086] Wherein, in step 201, the latest logic synthesis operation performed on the RTL design file is the first logic synth...

Embodiment 3

[0102] see Figure 4 , Figure 4 It is a structural schematic diagram of a logic synthesis control device disclosed in an embodiment of the present invention. in, Figure 4 The described device can be applied in an FPGA synthesis tool, and the FPGA synthesis tool can be combined with artificial intelligence to realize the application of FPGA in the field of artificial intelligence. Such as Figure 4 As shown, the logic synthesis control device may include:

[0103] The first detection module 301 is configured to detect whether the initial value of the memory in the read RTL design file has changed.

[0104] The modification module 302 is used to modify the netlist after the synthesis obtained by performing the logic synthesis operation on the RTL design file last time according to the pre-established mapping relationship when the first detection module 301 detects that the initial value of the memory in the RTL design file changes. The initial value of the memory instance...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More