Autonomous controllable data communication gateway machine based on double high-speed buses and communication method

A technology of a data communication network and a communication method, which is applied to an autonomously controllable data communication gateway based on dual high-speed buses and the field of communication, which can solve problems such as RAM access bottlenecks, achieve the effect of liberating performance bottlenecks and alleviating data processing capabilities

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

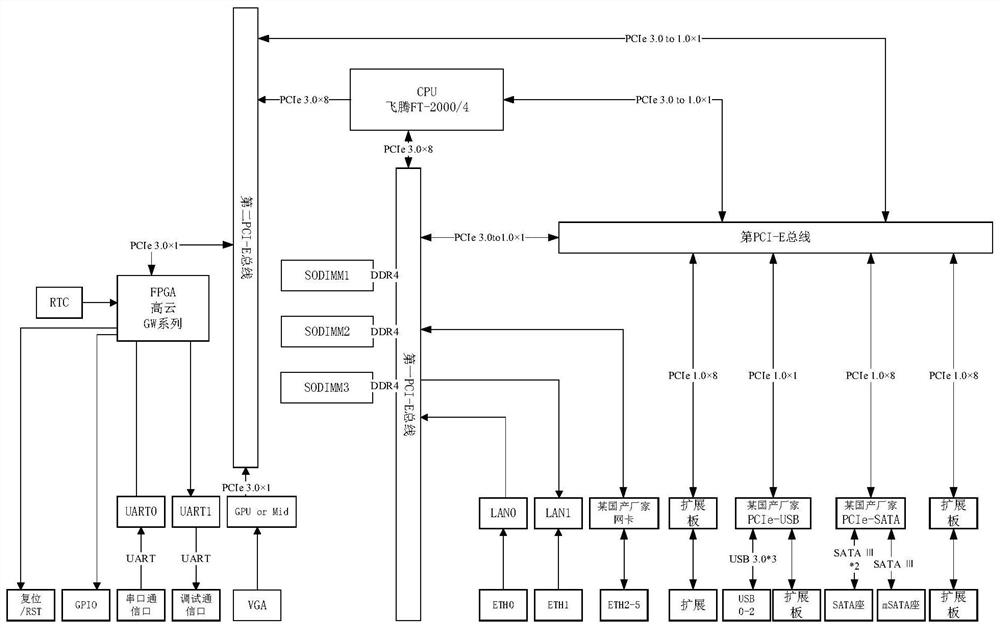

[0053] see figure 1 As shown, the present invention provides an autonomously controllable data communication gateway based on dual high-speed buses, including: a CPU, a first PCI-E bus, a second PCI-E bus and a third PCI-E bus. The first PCI-E bus is a high-speed bus of PCI-E3.0, the second PCI-E bus is a high-speed bus of PCI-E3.0, and the third PCI-E bus is a low-speed bus of PCI-E1.0.

[0054] The first PCI-E bus adopts FT PCI-E3.0 high-speed bus.

[0055] The first PCI-E bus (FT PCI-E3.0 high-speed bus) is connected to the CPU (FT2000+) through the PCI-E3.0×8 interface, and receives commands and returns data;

[0056] The first PCI-E bus (FT PCI-E3.0 high-speed bus) is connected to the domestic RAM through DDR4, and the cache data is read and written through Bank / Row Active and IO;

[0057] The first PCI-E bus (FT PCI-E3.0 high-speed bus) is connected with the domestic ETH0-5 through the network port LAN0-5 to process network requests and network data;

[0058] The firs...

Embodiment 2

[0070] The present invention also provides a communication method for an autonomously controllable data communication gateway based on dual high-speed buses. Based on the autonomously controllable data communication gateway based on dual high-speed buses described in Embodiment 1, the communication method includes:

[0071] The first PCI-E bus communicates with the random access memory RAM, and handles cache data reading and writing through Bank / Row Active and IO; the first PCI-E bus is dedicated to RAM access, and is used to solve the bottleneck of device access to RAM ;

[0072] The first PCI-E bus communicates with the network port to process network requests and network data;

[0073] The first PCI-E bus communicates with the third PCI-E bus, and receives the request and response of the low-speed response device collected by the third PCI-E bus to the random access memory RAM;

[0074] The first PCI-E bus communicates with the CPU, receives commands and returns data;

[...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More