Security authentication system and method for 3D stacked chips

A security certification and security verification technology, applied in the transmission system, electrical components, etc., can solve the problems of no 3D stacked chip security certification, and achieve the effect of providing security certification performance and high security

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

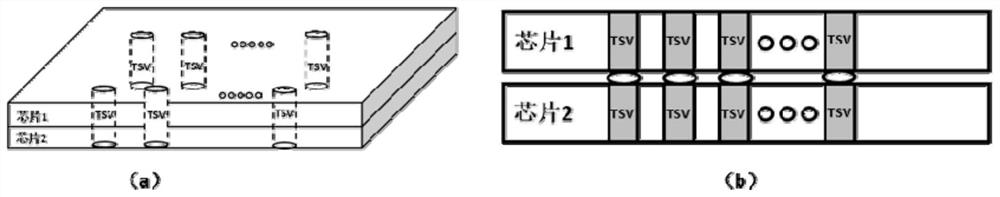

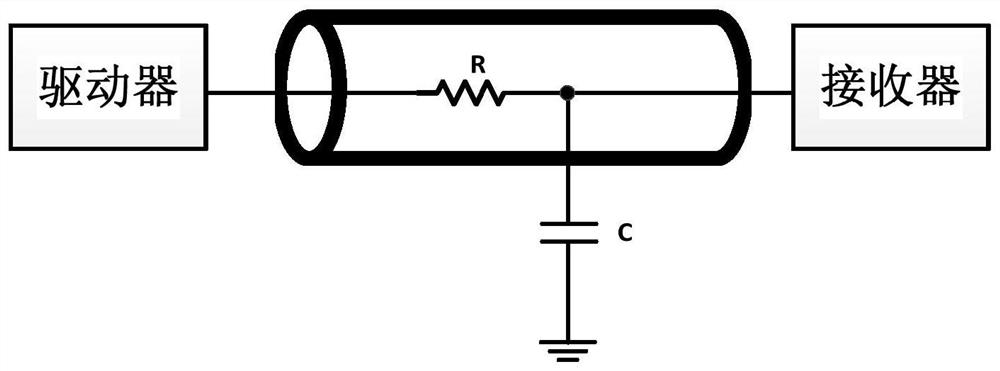

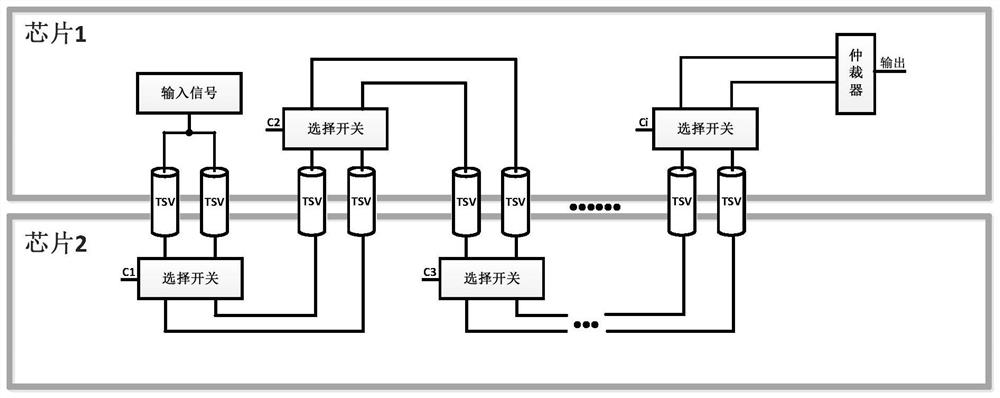

[0034] see figure 1 as well as figure 2 , the present invention provides a security authentication system for 3D stacked chips, including an arbiter PUF circuit and a first chip and a second chip stacked up and down, the first chip and the second chip are associated through a TSV path, and the arbitration The PUF circuit includes two parallel signal paths, the structures of the two signal paths are symmetrical, and path selection switches are arranged at intervals on the signal paths, the TSV paths are connected between the path selection switches, and the two The signal path is connected to the same signal input end, and the output end is connected to the arbiter.

[0035] Such as figure 1 Shown is a schematic diagram of the chip structure based on TSV stacking. Through the manufacture of TSV through holes in the middle of chip 1 and chip 2, the interconnection of chip 1 and chip 2 is realized to achieve the purpose of high speed, low power consumption and miniaturization....

Embodiment 2

[0043] A security authentication method for 3D stacked chips, using the security authentication system for 3D stacked chips in Embodiment 1, such as Image 6 shown, including steps:

[0044] S10. Apply an excitation signal to the arbiter PUF circuit, generate different excitation-response data based on different 3D stacked chips; upload the excitation-response data to the data center;

[0045] S20. Perform stimulus-response verification on the chip before the chip is used, obtain verification data and compare it with the stimulus-response data of the data center, and complete chip security verification.

[0046] Before step S10, a step signal needs to be input at the signal input terminal, which is transmitted simultaneously by the two signal paths; the step signals on the two signal paths respectively enter the path selection switch through the set TSV path.

[0047] Step S10 includes:

[0048] The step signal enters the path selection switch, and the arbiter PUF circuit ap...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More