Fully homomorphic encryption hardware accelerator based on systolic array and design method thereof

A hardware accelerator and fully homomorphic encryption technology, which is applied in the direction of homomorphic encryption communication, electrical components, secure communication devices, etc., can solve problems such as unsatisfactory real-time performance and increased encryption time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

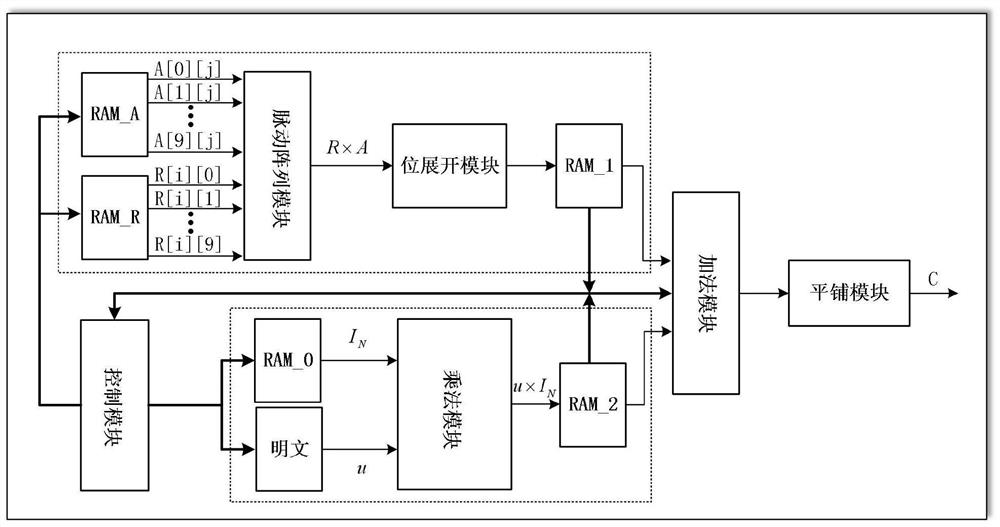

[0038] In this embodiment, a fully homomorphic encryption hardware accelerator based on a systolic array, such as figure 1 As shown, including: control module, systolic array module, bit expansion module, multiplication module, addition module, tiling module;

[0039] The control module controls the binary matrix R, the public key A, and the identity matrix I N and the input method of plaintext u, and store the first three data in RAM_R, RAM_A and RAM_0 respectively;

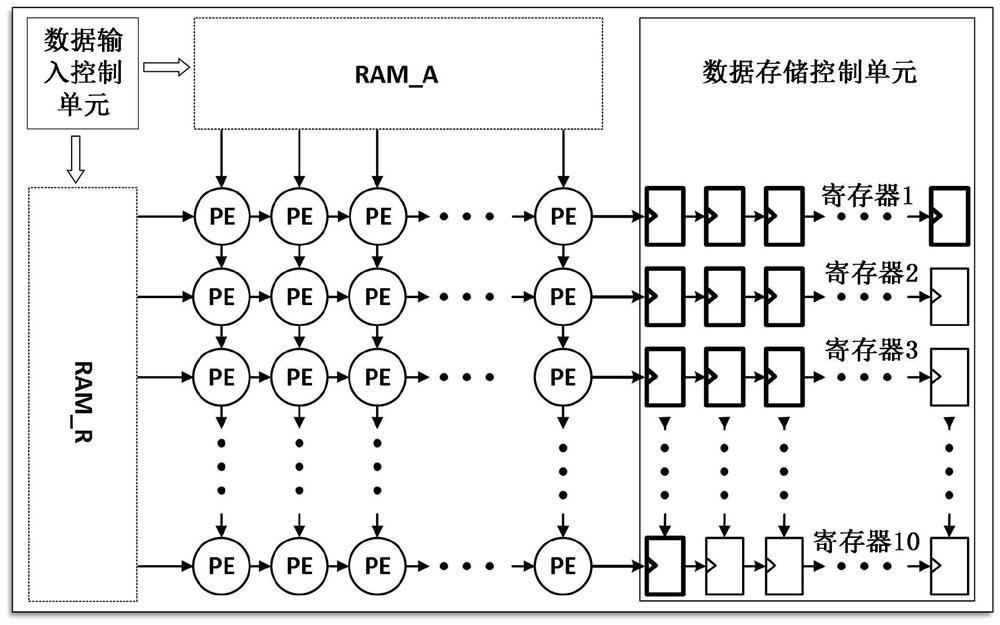

[0040] Systolic array modules such as figure 2 As shown, it consists of a data input control unit, a PE array, and a data storage control unit;

[0041] The data input control unit reads the first row of the binary matrix R from RAM_R, reads the first column of the public key A from RAM_A, and then transfers the read row and column of data to the PE array;

[0042]The PE array is composed of several PE units, and each PE unit is as image 3 As shown, it consists of a data selector, an adder, and a PE regist...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More