Forming method of transistor device layout

A transistor and layout technology, which is applied in the field of transistor device layout formation, can solve the problem of high power consumption in shadowed areas, and achieve the effects of reducing power consumption, avoiding shadowed areas, and reducing leakage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

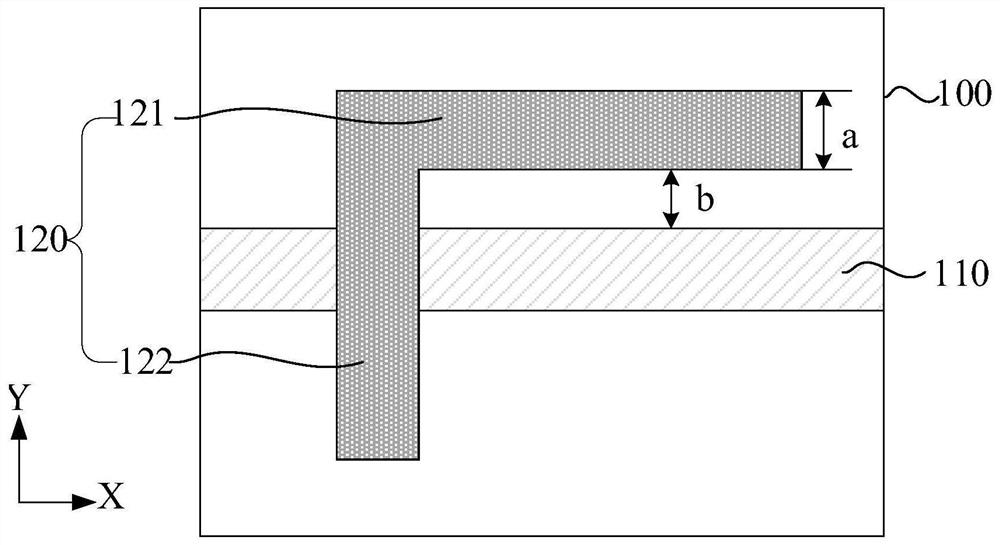

[0033] The method for forming the transistor device layout proposed by the present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments. The advantages and features of the present invention will become clearer from the following description. It should be noted that all the drawings are in a very simplified form and use imprecise scales, and are only used to facilitate and clearly assist the purpose of illustrating the embodiments of the present invention.

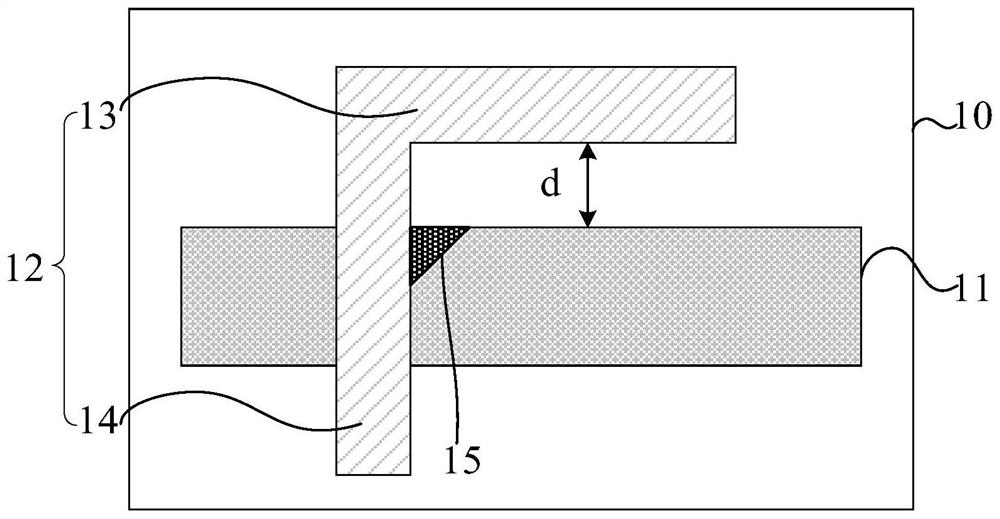

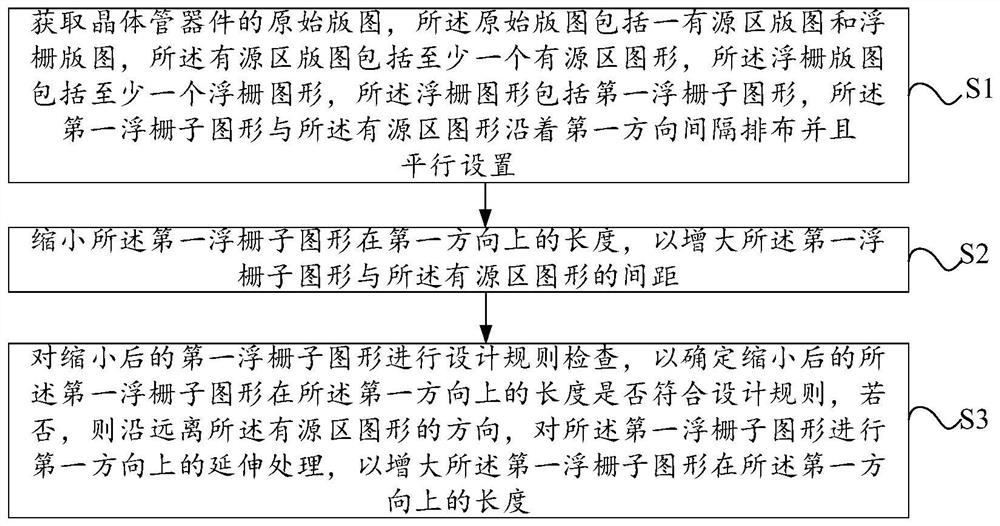

[0034] The inventors found that the reason why there is a shaded area in the active region of the existing transistor device is that in the manufacturing method of the transistor device, ion implantation is usually performed on the active region of the transistor device to form the source region and the drain region , if the distance between the first part of the floating gate and the active area is close, the first part of the floating gate will block th...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Size | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More