Multi-core processor and control method thereof

A multi-core processor and control method technology, applied in program control design, electrical digital data processing, instruments, etc., can solve problems such as affecting logic processing capability and slowing response, and achieve improved performance, improved overall performance, and sufficient data communication. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] The present invention will be further described in detail below in conjunction with specific embodiments, which are explanations of the present invention rather than limitations.

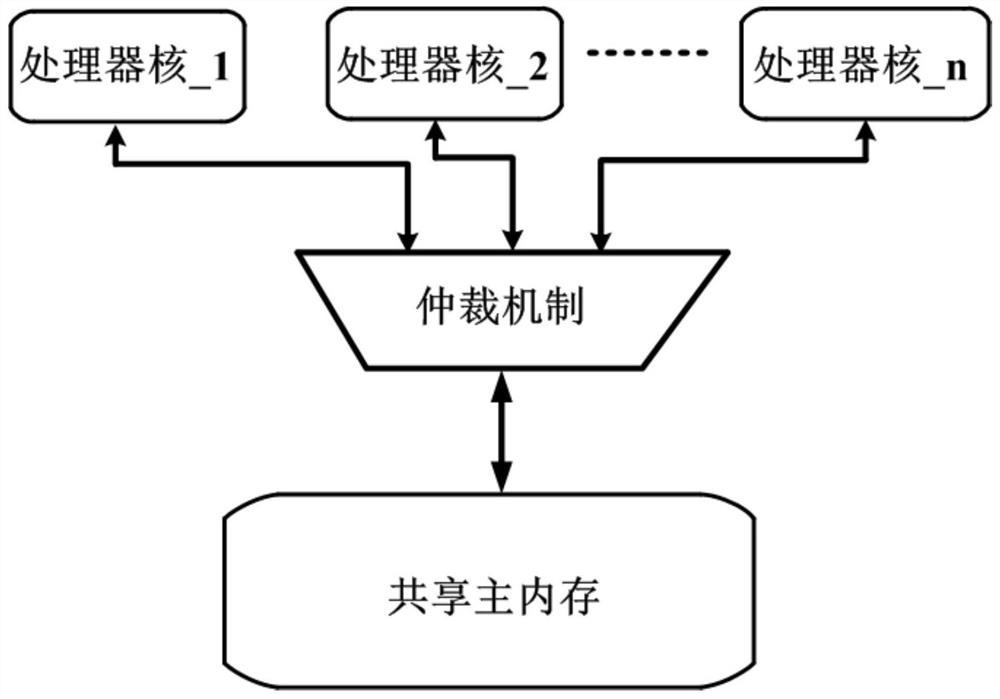

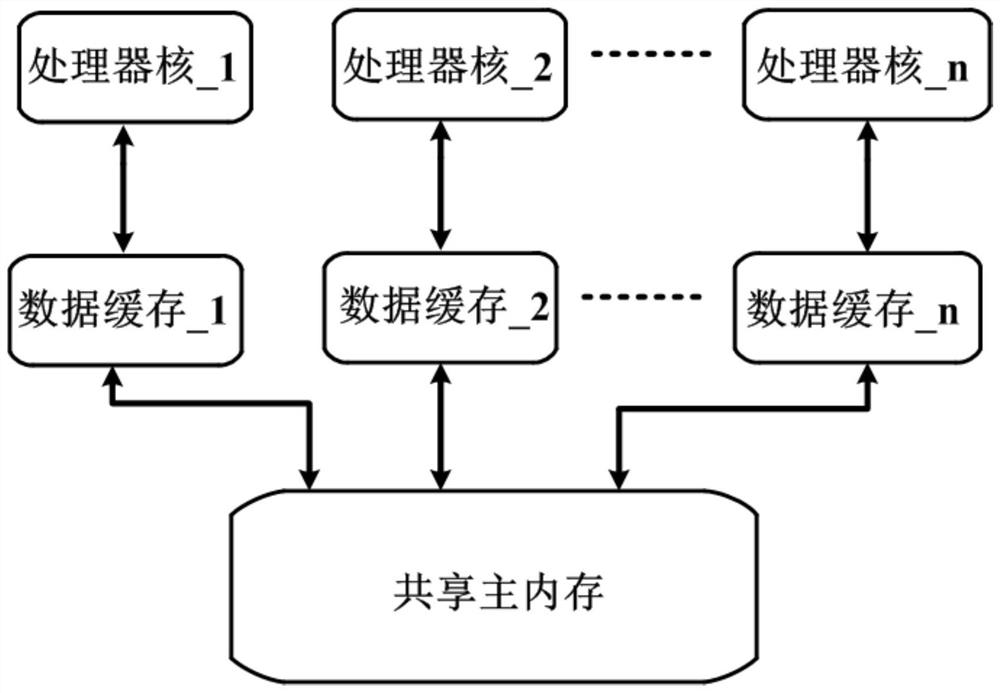

[0037] A kind of multi-core processor of the present invention comprises,

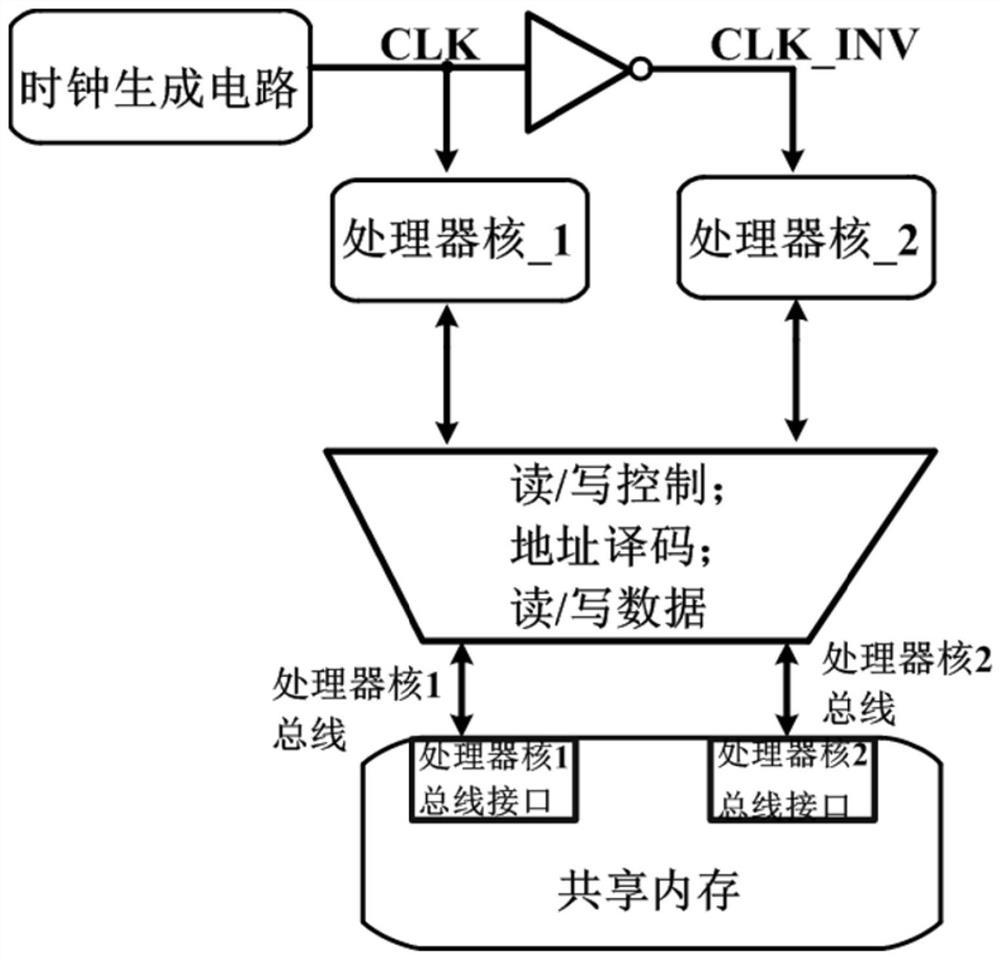

[0038] A pair of processor core A and processor core B;

[0039] The shared memory is used to connect the paired processor core A and processor core B respectively;

[0040] The clock generation circuit is configured to generate a clock signal; the clock signal is input to the processor core A, and is used as a working sequence of the processor core A to control the interaction with the shared memory;

[0041] The inverter is connected to the output end of the clock generating circuit, and is configured to invert the clock signal to generate an inverted clock signal; the inverted clock signal is input to the processor core B, and is used as the working sequence of the processor core B, and is controlled and Interact...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More