Electrostatic discharge protection circuit

A technology for electrostatic discharge protection and circuits, which is applied to circuits, electrical components, electric solid devices, etc., and can solve problems such as damage to the gate oxide layer

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] Preferred embodiments of the present invention will be described in detail below with examples shown in the accompanying drawings.

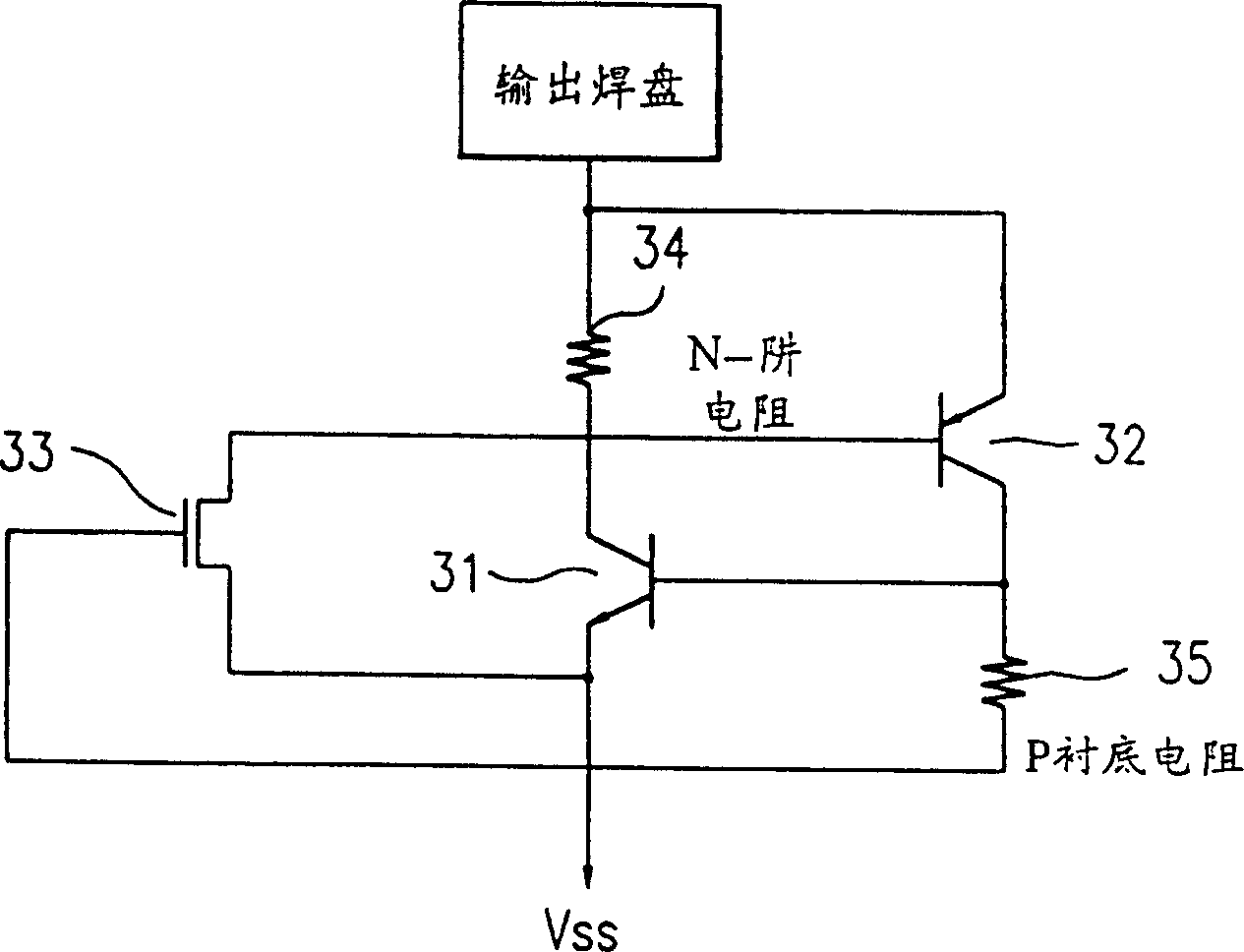

[0029] Figure 4A Represent the circuit configuration of the control gate SCR ESD protection circuit according to the present invention, Figure 4B is a cross-sectional view of a control gate SCR ESD protection circuit according to the present invention. see Figure 4A, the control gate SCR circuit includes: a first transistor 41 whose collector is connected to the output pad, the emitter of the first transistor 41 is connected to the Vss line; a second transistor 42 whose collector is connected to the base of the first transistor 41 , the emitter of the second transistor 42 is connected to the output pad; its source is connected to the MOS transistor 43 of the base of the second transistor 42, the drain of the MOS transistor 43 is connected to the emitter of the first transistor 41, the MOS transistor 43 The control gate is connected t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More