Method and structure for measuring photoetching overlay error before and after epitaxy

A photolithography overlay and error technology, applied in semiconductor/solid-state device testing/measurement, optics, and patterned surface photoengraving process, etc., can solve the problem of inability to accurately measure the offset before and after epitaxy, and eliminate expansion blur. , the effect of precise lithography overlay error

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

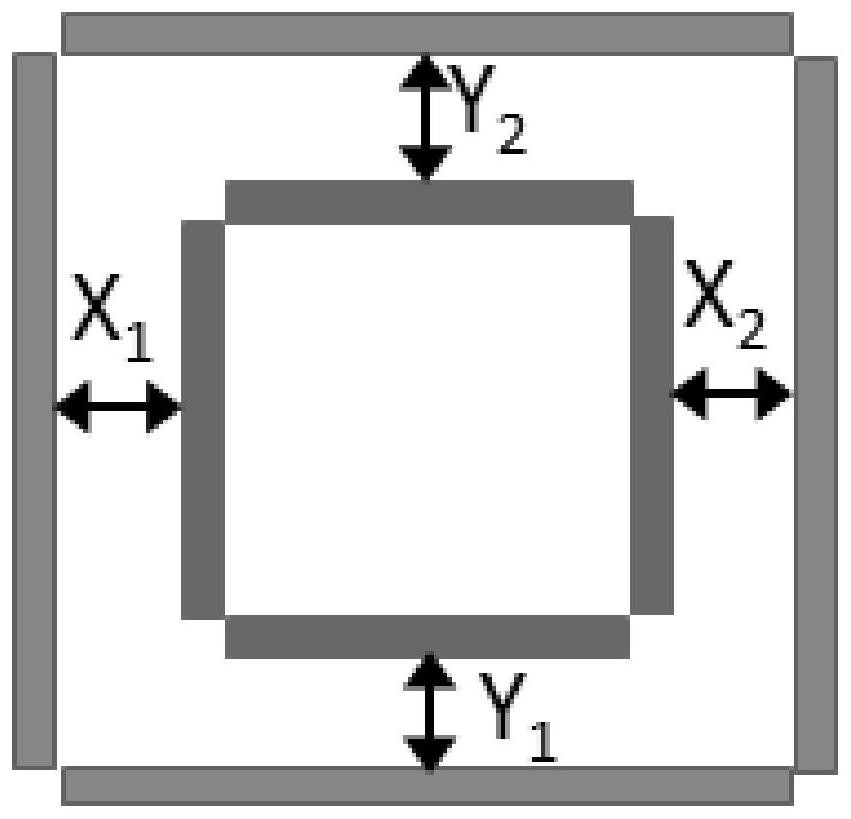

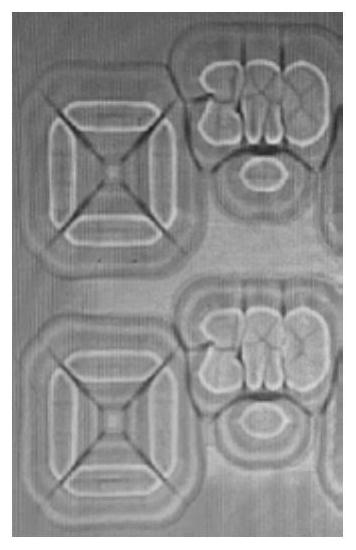

[0033] The method and structure for measuring the overlay error before and after epitaxy proposed by the present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments. Advantages and features of the present invention will be apparent from the following description and claims. It should be noted that all the drawings are in a very simplified form and use imprecise scales, and are only used to facilitate and clearly assist the purpose of illustrating the embodiments of the present invention.

[0034] In addition, unless otherwise stated, features in different embodiments of the present invention can be combined with each other. For example, a feature in the second embodiment may be used to replace a corresponding or functionally identical or similar feature in the first embodiment, and the resulting embodiment also falls within the scope of disclosure or description of the present application.

[0035] The cor...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More