On-chip measurement method and system for electromagnetic immunity of SRAM

An electromagnetic immunity and on-chip measurement technology, applied in static memory, instruments, etc., can solve the problem of not being able to accurately obtain the interference range of the internal power supply pad, SRAM read and write separately, and achieve the effect of occupying a small chip area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

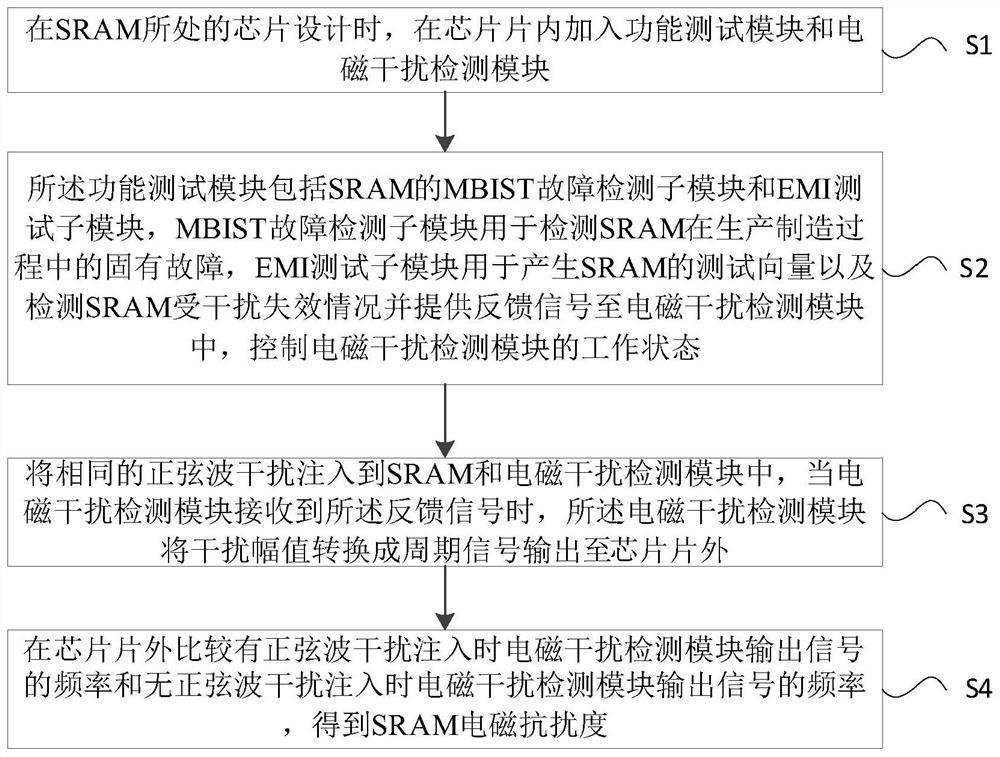

[0051] This embodiment provides an on-chip measurement method of SRAM electromagnetic immunity, such as image 3 , including the following steps:

[0052] S1: When designing the chip where the SRAM is located, add a functional test module and an electromagnetic interference detection module to the chip;

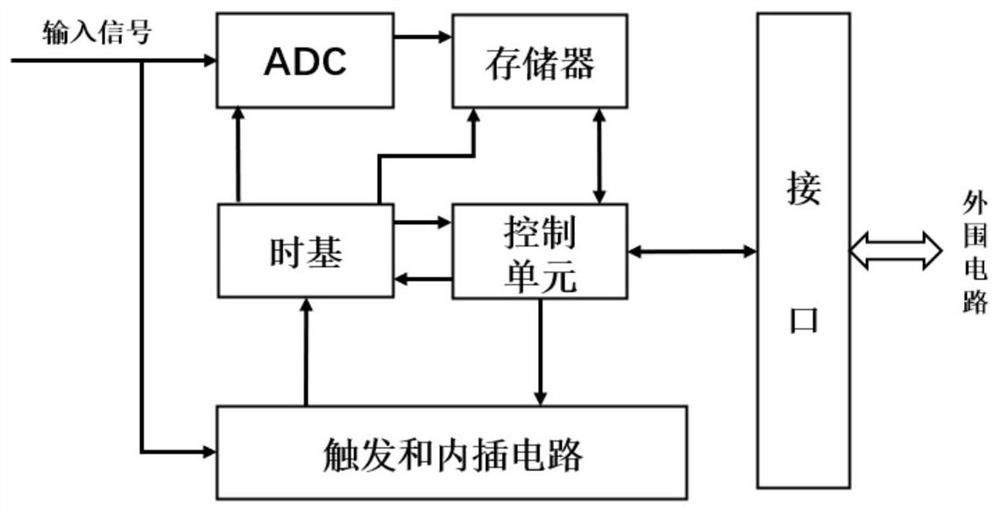

[0053] S2: The functional test module includes a MBIST fault detection sub-module and an EMI test sub-module, the MBIST fault detection sub-module is used to detect inherent faults in the SRAM manufacturing process, and the EMI test sub-module is used to generate SRAM test vectors and detect The SRAM is disturbed and fails and provides a feedback signal to the electromagnetic interference detection module to control the working state of the electromagnetic interference detection module;

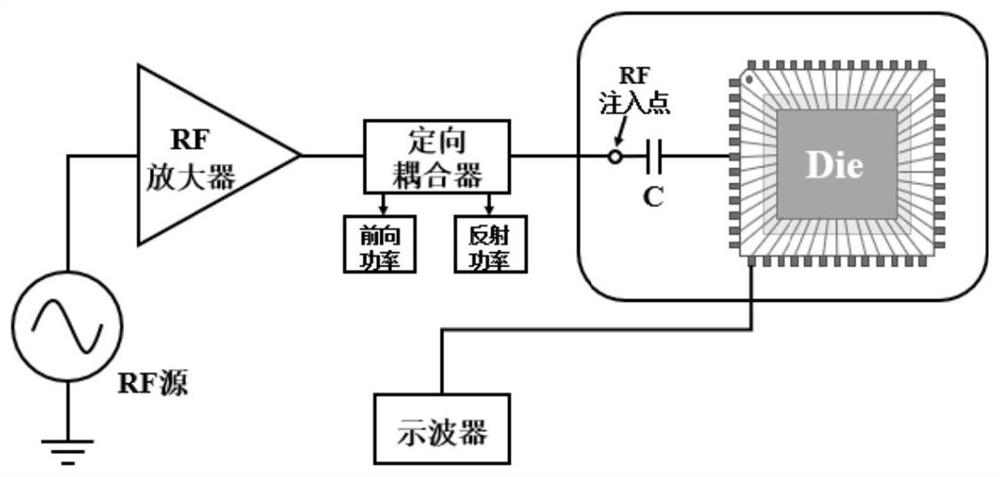

[0054] S3: Inject the same sine wave interference into the SRAM and the electromagnetic interference detection module. When the electromagnetic interference detection module receives the fe...

Embodiment 2

[0073] This embodiment provides an on-chip measurement system of SRAM electromagnetic immunity, including:

[0074] Described function test module comprises MBIST failure detection submodule and EMI test submodule, and MBIST failure detection submodule is used for detecting the inherent failure of SRAM in the manufacturing process, and EMI test submodule is used for generating the test vector of SRAM and detecting SRAM affected Interference failure and provide feedback signals to the electromagnetic interference detection module to control the working status of the electromagnetic interference detection module

[0075] A power supply interference detection module, the power supply interference detection module is arranged in the chip, and the same sine wave interference is injected into the SRAM and the electromagnetic interference detection module. When the electromagnetic interference detection module receives the feedback signal, the electromagnetic interference detection mo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More