A Miniaturized ldpc Encoder Circuit Based on Code Rate Adaptation

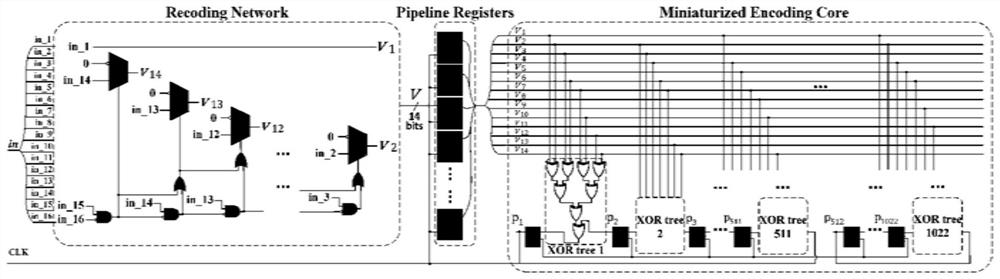

An adaptive and encoder technology, applied in the field of logic circuits, can solve the problems that restrict the development of miniaturized application scenarios, it is difficult to support code rate adaptive technology, and the throughput is not high enough.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example 1

[0056] Example 1 A digital communication system based on a miniaturized LDPC encoder architecture wherein the code rate under the current log-likelihood ratio is 7 / 8

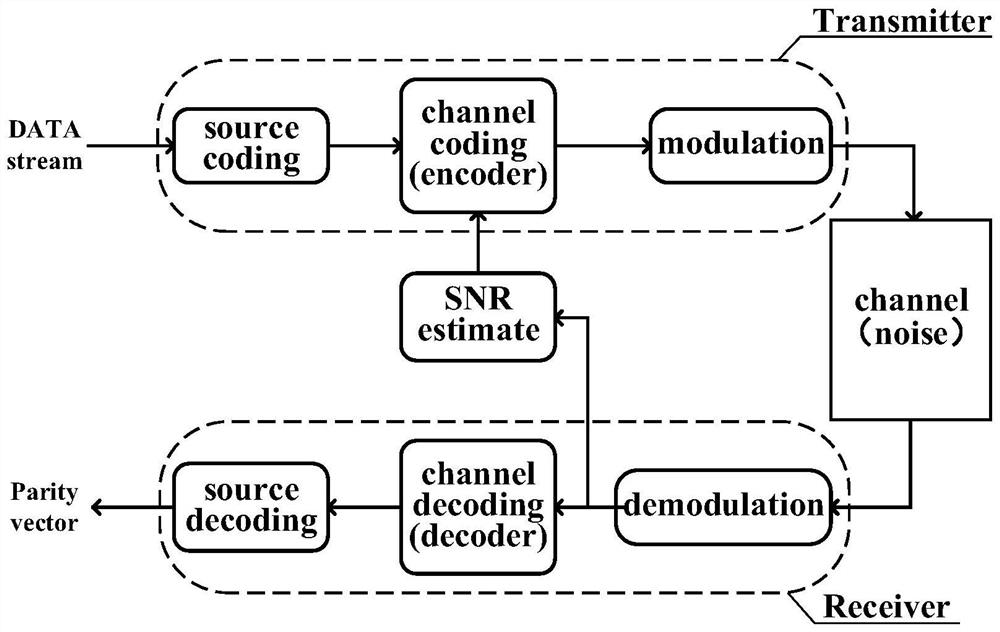

[0057] by image 3 An example of a simple digital communication system:

[0058] 1) The input data stream is processed by the transmitter (Transmitter) and sent to the receiver (Receiver);

[0059] 2) After the signal-to-noise ratio (SNR) is acquired by the encoder, the log-likelihood ratio of the input data is evaluated, and the corresponding corresponding code rate r=7 / 8 is selected;

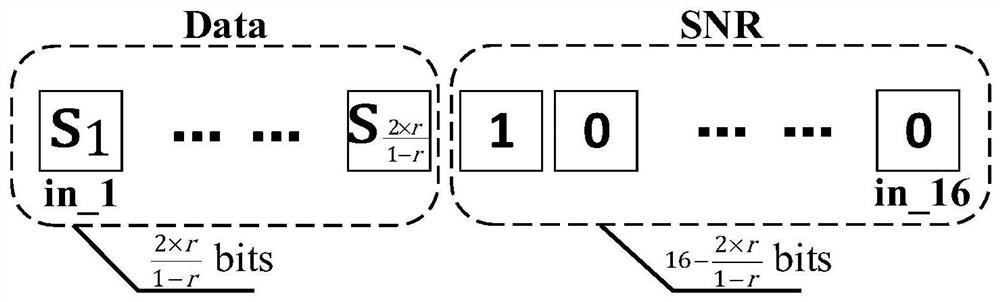

[0060] 3) According to the code rate r=7 / 8, it can be known that the input of the architecture must meet the following conditions: the total number of input bits and the signal-to-noise ratio is 16 bits, the bit width of the data to be encoded is 14 bits, and the bit width of the signal-to-noise ratio is 2 bits. ;

[0061] 4) The input data is cleared by the re-encoding network in the miniaturized LDPC encoder architecture to...

example 2

[0064] Example 2 A digital communication system based on a miniaturized LDPC encoder architecture wherein the code rate under the current signal-to-noise ratio is 4 / 5

[0065] by image 3 An example of a simple digital communication system:

[0066] 1) The input data stream is processed by the transmitter (Transmitter) and sent to the receiver (Receiver);

[0067] 2) After the signal-to-noise ratio (SNR) is obtained by the encoder, the log-likelihood ratio of the input data is evaluated, and the corresponding corresponding code rate r=4 / 5 is selected;

[0068] 3) According to the code rate r=4 / 5, it can be known that the input of the architecture must meet the following conditions: the total number of input bits and signal-to-noise ratio is 16 bits, the bit width of the data to be encoded is 8 bits, and the bit width of the signal-to-noise ratio is 8 bits. ;

[0069] 4) The input data is cleared by the re-encoding network in the miniaturized LDPC encoder architecture to cle...

example 3

[0072] Example 3 A digital communication system based on a miniaturized LDPC encoder architecture wherein the code rate under the current signal-to-noise ratio is 2 / 3

[0073] by image 3 An example of a simple digital communication system:

[0074] 1) The input data stream is processed by the transmitter (Transmitter) and sent to the receiver (Receiver);

[0075] 2) After the signal-to-noise ratio (SNR) is acquired by the encoder, the log-likelihood ratio of the input data is evaluated, and the corresponding corresponding code rate r=2 / 3 is selected;

[0076] 3) According to the code rate r=2 / 3, it can be known that the input of the architecture must meet the following conditions: the total number of input bits and the signal-to-noise ratio is 16 bits, the bit width of the data to be encoded is 4 bits, and the bit width of the signal-to-noise ratio is 12 bits. ;

[0077] 4) The input data is cleared by the re-encoding network in the miniaturized LDPC encoder architecture t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More