SOC verification system and method based on UVM

A verification system and system-on-chip technology, applied in the field of UVM-based SOC verification system, to achieve the effect of ensuring correctness, avoiding repeated development, and ensuring test flexibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

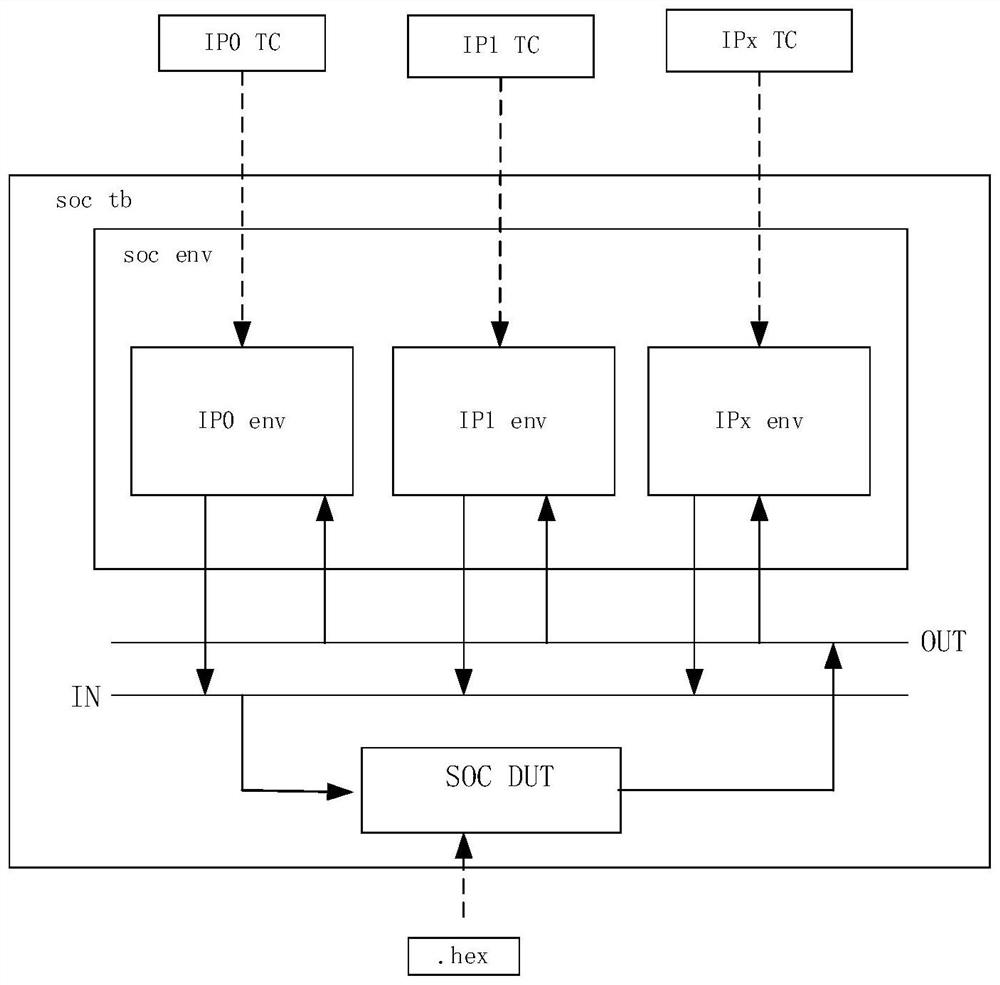

[0025] The verification object in this embodiment is a high-performance and low-power general-purpose system-on-chip SOC with risc-v as the core. There are buses AXI (Advanced Extensible Interface), AHB (Advanced Highperformance Bus), and APB (Advanced Peripheral Bus) in the system-on-chip SOC. The bus AXI is an on-chip bus for high performance, high bandwidth, and low latency. The bus AHB is mainly used for connection between high-performance modules (such as CPU, DMA and DSP, etc.). The bus APB is mainly used for the connection between low-bandwidth peripherals, such as UART, 1284, etc.

[0026] Specifically, different IPs are connected to corresponding buses according to bus characteristics and IP performance requirements. DDR and DMA modules are hung on the AXI bus, USB and Ethernet IPs are hung on the AHB bus, and IIC / UART / SPI and other IPs are hung on the APB bus.

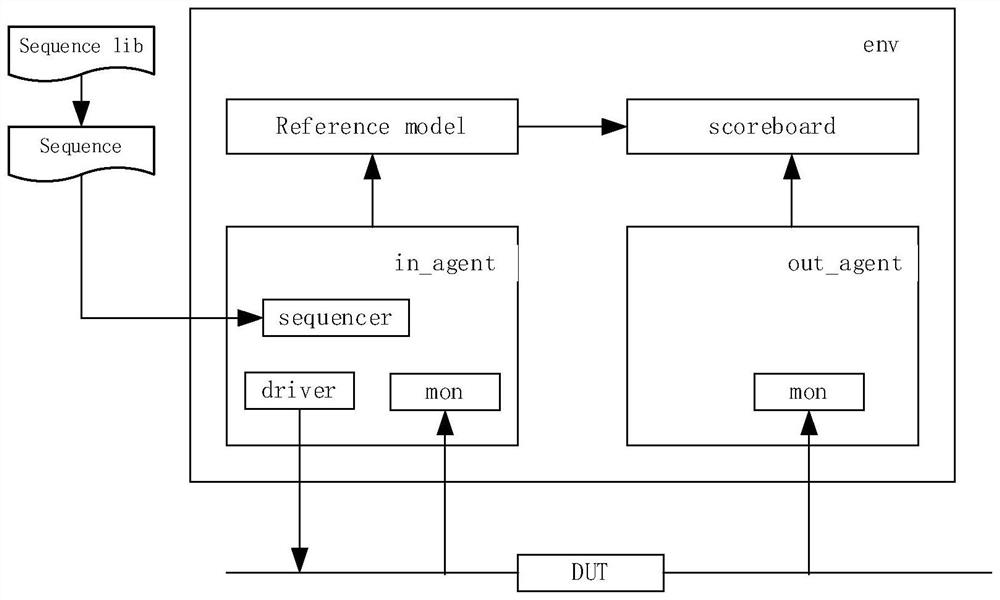

[0027] This embodiment proposes a UVM-based SOC verification system, including randomly generated test ...

Embodiment 2

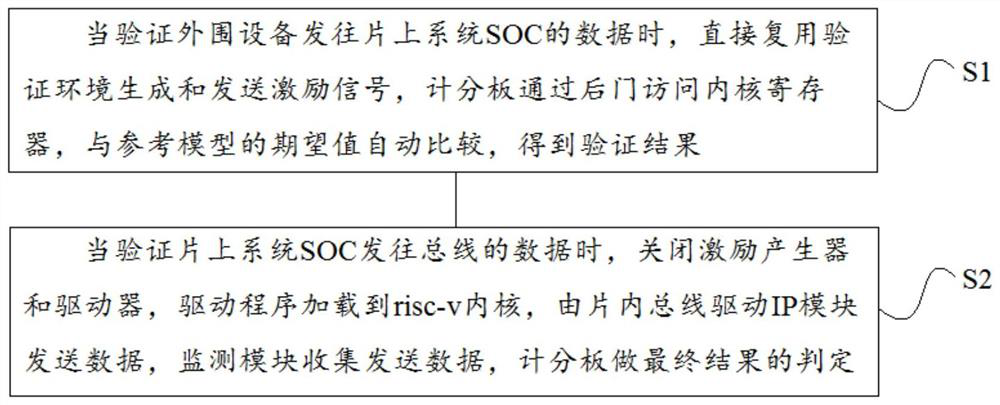

[0039]Based on the UVM-based SOC verification system proposed in Embodiment 1, correspondingly, in terms of methods, this Embodiment 2 proposes a UVM-based SOC verification method, such as image 3 As shown, it specifically includes the following steps:

[0040] S1: When verifying the data sent by the peripheral equipment to the SOC of the system on chip, the verification environment is directly multiplexed to generate and send the stimulus signal, and the scoreboard accesses the core register through the back door, and automatically compares with the expected value of the reference model to obtain the verification result;

[0041] S2: When verifying the data sent by the SOC to the bus, the stimulus generator and driver are turned off, the driver is loaded into the risc-v kernel, the on-chip bus drives the IP module to send data, the monitoring module collects and sends data, and the scoreboard performs Judgment of the final result.

[0042] The technical solutions and techni...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More