Three-dimensional integrated high-efficiency heat dissipation packaging structure and preparation method thereof

A packaging structure and high-efficiency technology, which is applied in the manufacture of semiconductor/solid-state devices, electric solid-state devices, semiconductor devices, etc., can solve problems such as high cost, high technical difficulty, and failure to consider the air cavity of microwave power chips, so as to meet electromagnetic compatibility The effect of sexual demands

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

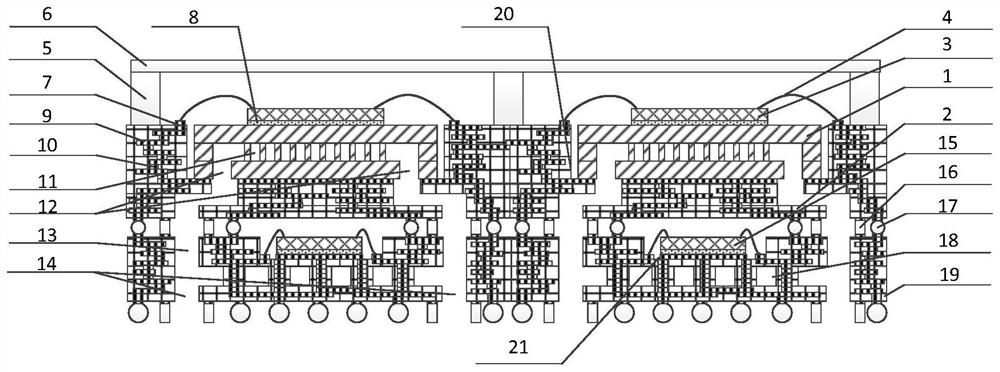

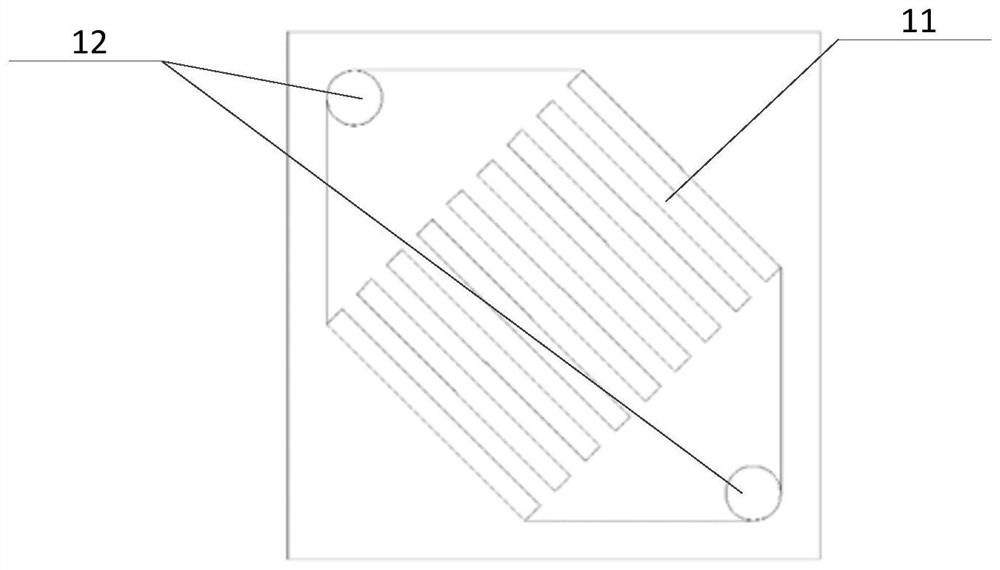

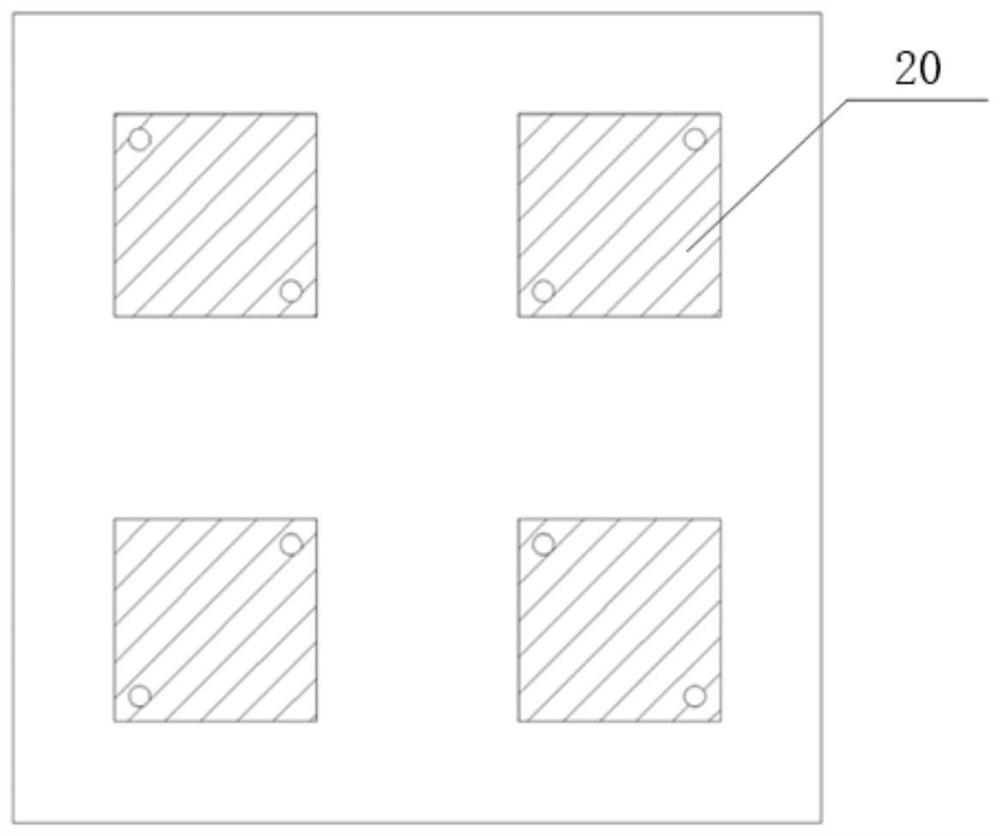

[0037] The present invention will be further described below in conjunction with the accompanying drawings.

[0038] Such as Figure 1-Figure 5 As shown, a three-dimensional integrated high-efficiency heat dissipation packaging structure includes: a first packaging substrate 2, a second packaging substrate 19, a heat dissipation microchannel 1, a first chip 3, a second chip 15, a cover plate 6, a surrounding frame 5, Liquid cooling connector 16 and electrical connector 17;

[0039] The heat dissipation micro-channel 1 and the surrounding frame 5 are welded on the first packaging substrate 2;

[0040] The first chip 3 is welded on the heat dissipation micro-channel 1 and interconnected with the surface pad of the first package substrate 2; the second chip 15 is welded on the second package substrate 1 and connected with the surface pad of the second package substrate 19 interconnected;

[0041] The cover plate 6 is welded on the surrounding frame 5 for sealing;

[0042] The...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More