Packaging structure formed by stacking multiple interconnected flip chips and preparation method thereof

A technology of flip-chip and packaging structure, which is applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc. It can solve the problems of large packaging structure area and inability to stack, and achieve miniaturization, size reduction, and reduction Effect of Area Utilization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

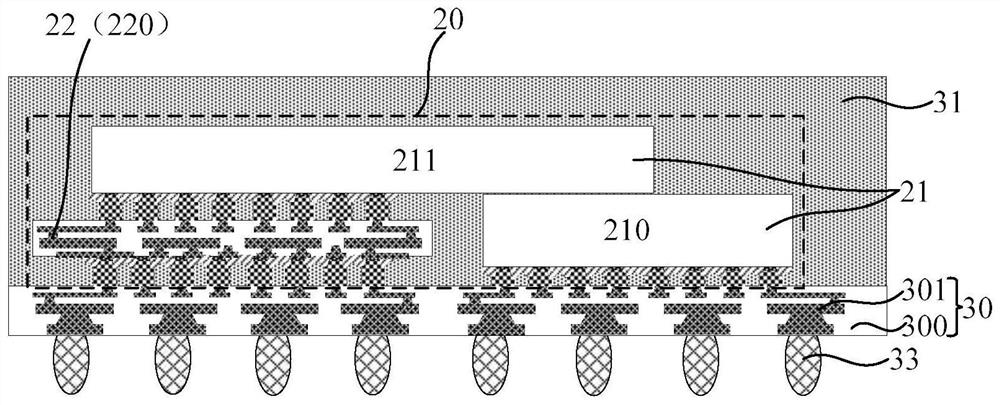

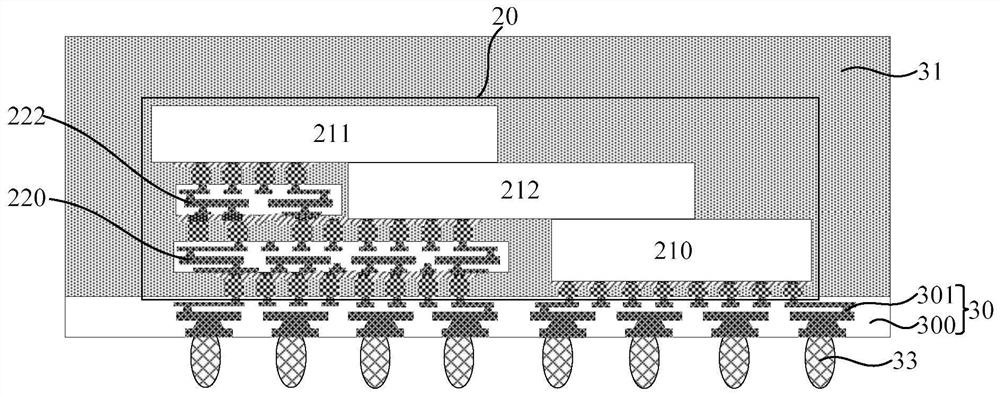

[0058] Such as Figure 2 to Figure 5 As shown, this embodiment provides a package structure of multiple interconnected flip-chip stacks, the package structure comprising:

[0059] The rewiring layer 30 is arranged on the bottom layer;

[0060] The flip chip stacking structure 20 is stacked on the upper surface of the rewiring layer 30 along the vertical direction; the flip chip stacking structure 20 includes N layers of flip chips 21 and N-1 layers of interposers 22, N≥2 ; Wherein, the first layer flip chip 210 and the first layer adapter board 220 are welded on the rewiring layer 30, the Mth layer adapter board 221 is welded on the M-1 layer adapter board 222, the Mth layer The layer flip chip 211 is stacked on the M-1 layer flip chip 212 and the M-1 layer adapter plate 222, and is non-electrically connected with the M-1 layer flip chip 212, Electrically connected to the M-1th layer adapter board 222, N≥M≥2;

[0061] The encapsulation layer 31 covers the flip chip stack st...

Embodiment 2

[0071] Such as Figure 6 to Figure 13 As shown, this embodiment provides a method for preparing a package structure of interconnected multiple flip-chip stacks, and the package structure of interconnected multiple flip-chip stacks described in the first embodiment can be manufactured by this preparation method. However, it is not limited thereto. For the beneficial effects it can achieve, please refer to Embodiment 1, which will not be repeated here.

[0072] Specifically, such as Image 6 Shown, described preparation method comprises the following steps:

[0073] S1, preparing the rewiring layer and the adapter board;

[0074] S2, stacking a flip-chip stacking structure vertically on the upper surface of the rewiring layer, the flip-chip stacking structure includes N layers of flip chips and N-1 layers of interposer boards, N≥2, including: The first layer of flip chip and the first layer of the adapter board are welded on the rewiring layer; the Mth layer of the adapter bo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More