Digital test vector automatic learning method and system

A technology of automatic learning and digital testing, applied in the field of electronics, can solve the problems of complex logic chip vector programming difficulty and low debugging efficiency, so as to save writing time and efficiency, improve development efficiency, and reduce programming difficulty.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] Below in conjunction with accompanying drawing and specific embodiment, further illustrate the present invention, should be understood that these examples are only for illustrating the present invention and are not intended to limit the scope of the present invention, after having read the present invention, those skilled in the art will understand various aspects of the present invention All modifications of the valence form fall within the scope defined by the appended claims of the present application.

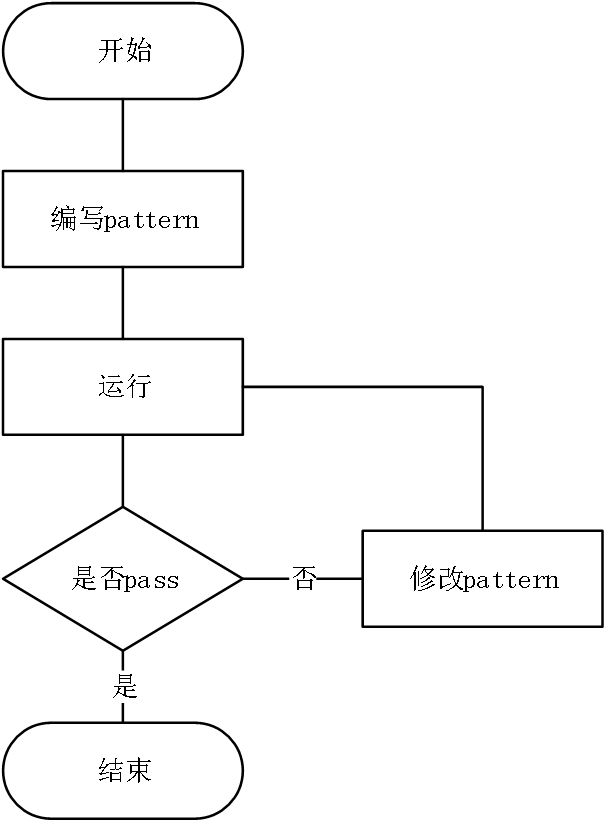

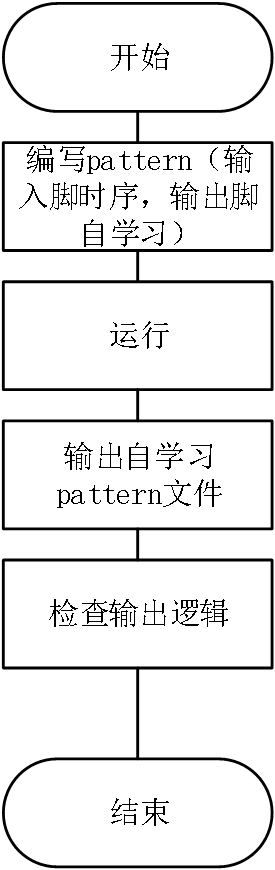

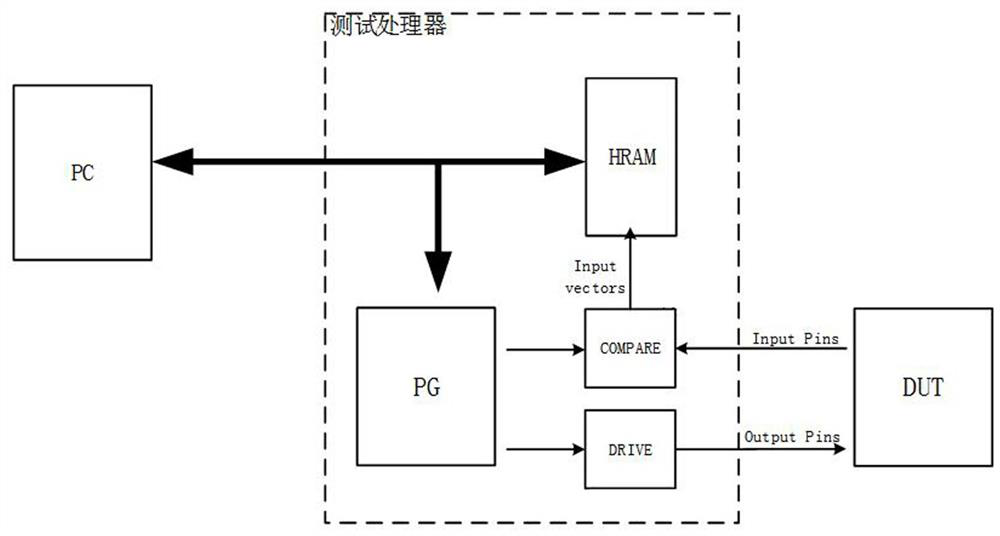

[0036] A method for automatic learning of digital test vectors, such as Figure 2-7 shown, including the following steps:

[0037] Step 1. Write a graphic file. The graphic file includes input pin timing and output pin timing. The input pin timing is given by the device under test, and the input pin timing includes clock timing, driving data timing, and enable signal timing. The timing of the output pin is set to the learning state. When writing the pattern graphic...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More