In-memory operation method and device and application thereof

A computing method and technology of computing units, which are applied to in-memory computing, devices and their application fields, can solve the problems that computing results are easily affected by noise, area waste, etc., so as to increase the cost of circuit area, ensure high efficiency, and high computing energy efficiency. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0086] Please refer to Figure 1-6 , an in-memory computing method of this embodiment, comprising:

[0087] The storage array is divided and configured into several basic operation blocks according to the single-channel operation function. The storage array can be one of NOR Flash storage array, ReRAM storage array, SRAM storage array or DRAM storage array. As for which storage array to choose for implementation The structure of the computing unit of the present invention is all all can, and technician can select according to need, therefore in this embodiment take NOR Flash storage array as example to carry out further introduction;

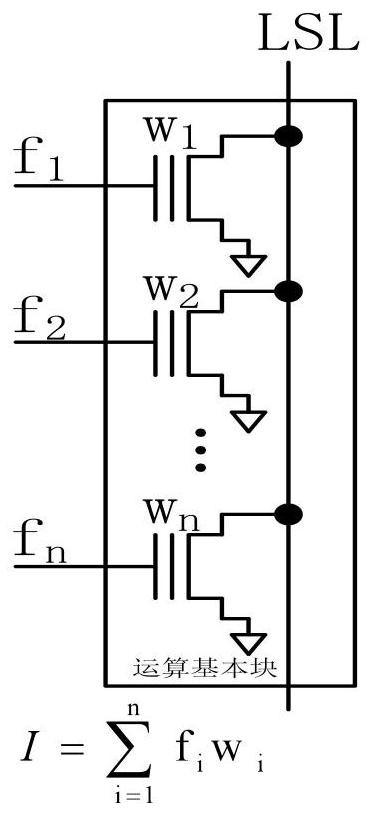

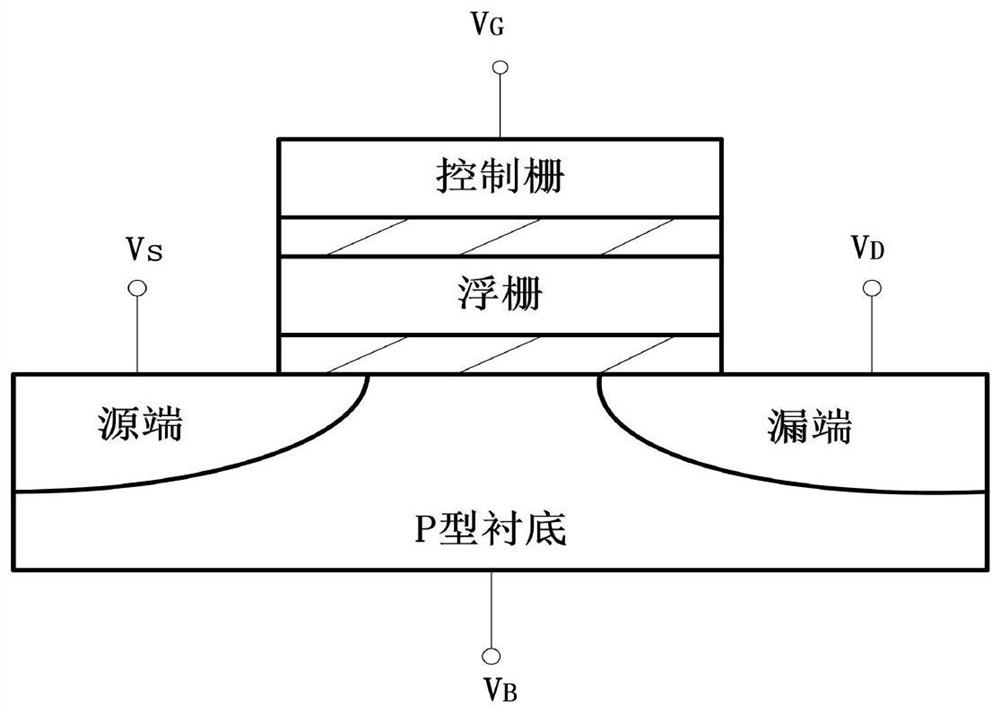

[0088] The output terminals of all the operation units in the operation basic block are connected to the matching local summation line LSL, such as figure 1 As shown, in this embodiment, the operation unit is a single storage unit, and a single storage unit is also a single floating gate field effect transistor such as figure 2 As shown, the ...

Embodiment 2

[0101] An in-memory computing method in this embodiment is similar to the in-memory method in embodiment 1, the main difference is that the composition of the computing unit is different, so the similarities in this embodiment and embodiment 1 will not be repeated, please refer to the embodiment Contents in 1;

[0102] An in-memory computing method provided in this embodiment includes:

[0103] The storage array is divided and configured into several computing basic blocks according to the single-channel operation function, wherein the storage array can be one of a NOR Flash storage array, a ReRAM storage array, an SRAM storage array or a DRAM storage array, and in this embodiment, the NOR The Flash storage array is taken as an example for further introduction;

[0104] Connect the output terminals of all the operation units in the operation basic block to the matching local summation line LSL, please refer to Figure 7 , in this embodiment, the operation unit is a combinati...

Embodiment 3

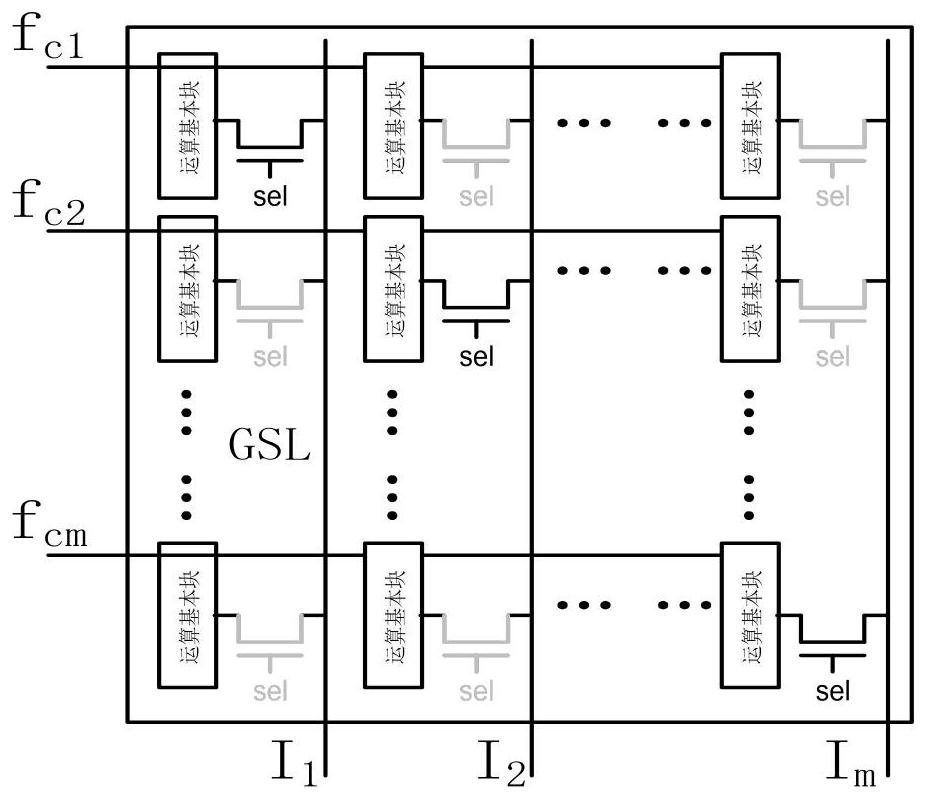

[0122] Please refer to Figure 12 , this embodiment provides an in-memory computing device, which is set to match the in-memory computing method in Embodiment 1, so some of the same content in this embodiment is the same as in Implementation 1, please refer to Embodiment 1, The in-memory operation device of this embodiment includes an operation array, an input module, a DAC module, a clock module, an SEL control module, a controller module, an ADC module and a shift selection module arranged in cooperation with each other;

[0123] The operation array is composed of several operation basic blocks, summation line LSL, summation line GSL and controlled switches, wherein the output terminals of all operation units in the operation basic block are connected to the local summation line LSL in a normalized manner, and each of the operation units located in the same column The summation line LSL is respectively connected to the summation line GSL data set by column through the contro...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More