Computing device, integrated circuit chip, board card, electronic equipment and computing method

A computing device and technology, applied in the field of computing, can solve problems such as hardware efficiently completing computing tasks, and achieve the effect of expanding application scenarios, adaptability, and efficient execution

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example 1

[0100] Example 1: TMUADCO=MULT+ADD+RELU(N)+CONVERTFP2FIX (7)

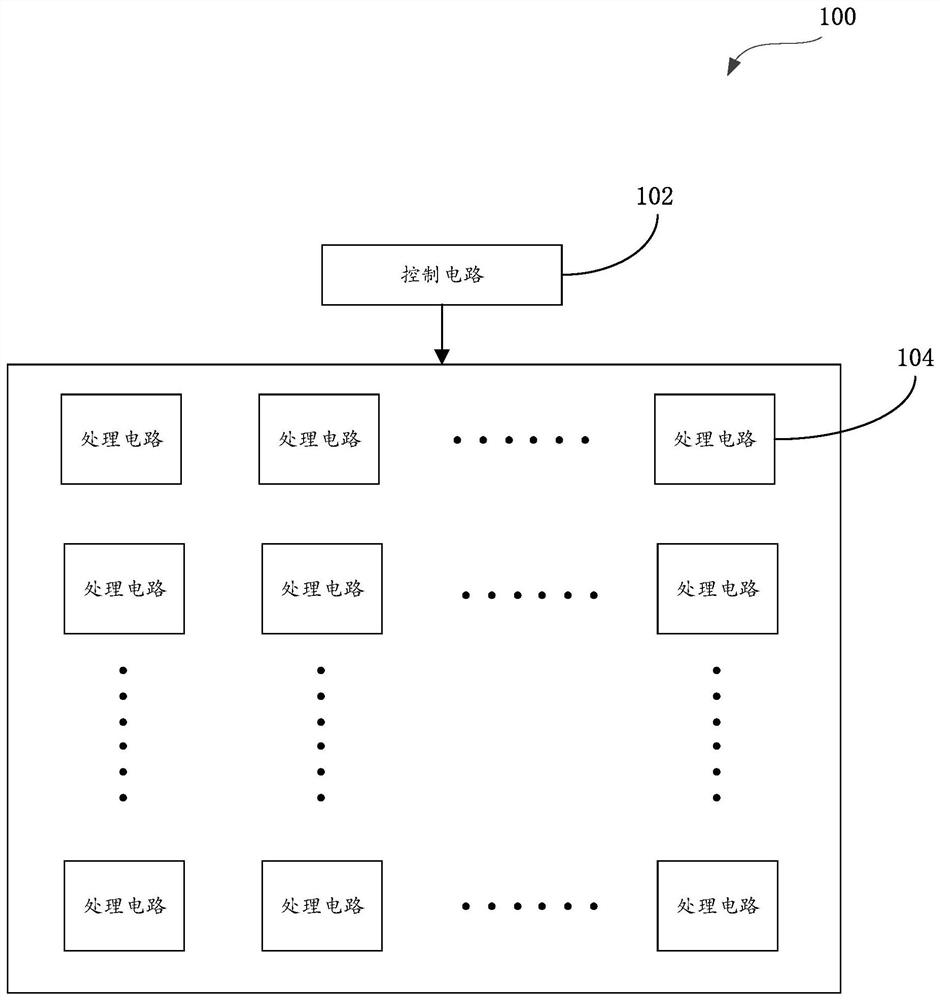

[0101] The instruction expressed in the above formula (7) is a calculation instruction that inputs a ternary operand and outputs a 1-element operand, and it can be composed of a three-stage pipeline operation (that is, multiplication+addition+activation) according to the present disclosure. ) processing circuit matrix to complete. Specifically, the ternary operation is A*B+C, in which the microinstruction of MULT completes the multiplication operation between the operands A and B to obtain the product value, that is, the first-level pipeline operation. Then, the ADD microinstruction is executed to complete the addition operation of the aforementioned product value and C to obtain the sum result “N”, that is, the second-stage pipeline operation. Then, the activation operation RELU is performed on the result, that is, the third-level pipeline operation. After the three-stage pipeline operation, the microinstruction...

example 2

[0102] Example 2: TSEADMUAD = SEARCHADD + MULT + ADD (8)

[0103] The instruction expressed in the above formula (8) is a calculation instruction that inputs a ternary operand and outputs a 1-ary operand, and it includes a two-stage pipeline operation (that is, multiplication+addition) that can be performed according to the present disclosure. The processing circuit matrix to complete the microinstructions. Specifically, the ternary operation is A*B+C, and the microinstruction of SEARCHADD can be completed by the pre-operation circuit to obtain the table lookup result A. Next, the multiplication operation between the operands A and B is completed by the first-stage pipeline operation to obtain the product value. Here, the operands A, B and the product value may be tensors read and saved according to the descriptors of the present disclosure. Then, the ADD microinstruction is executed to complete the addition operation of the aforementioned product value and C to obtain the s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More