Composite memory structure

A memory and composite technology, applied in the direction of semiconductor devices, electric solid devices, electrical components, etc., can solve the problem of low bit density of memory components, and achieve the effect of increasing bit density and improving reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

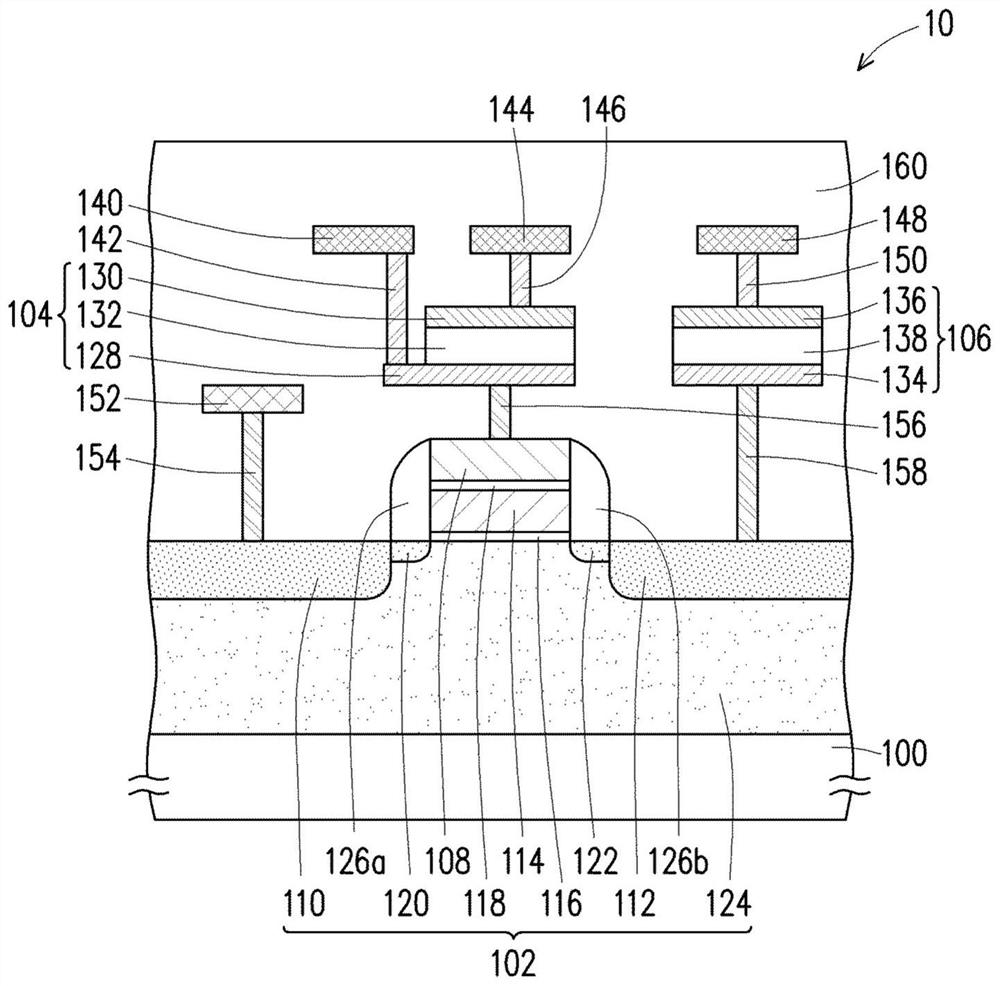

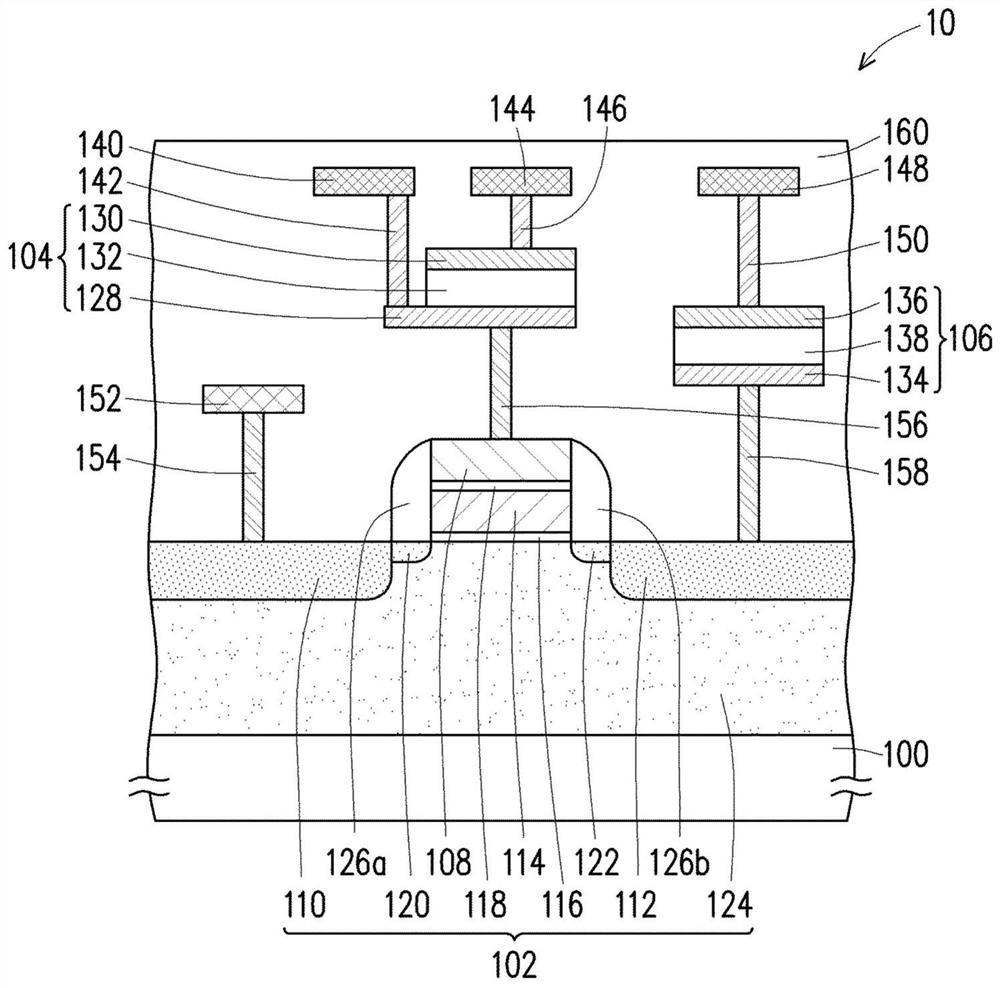

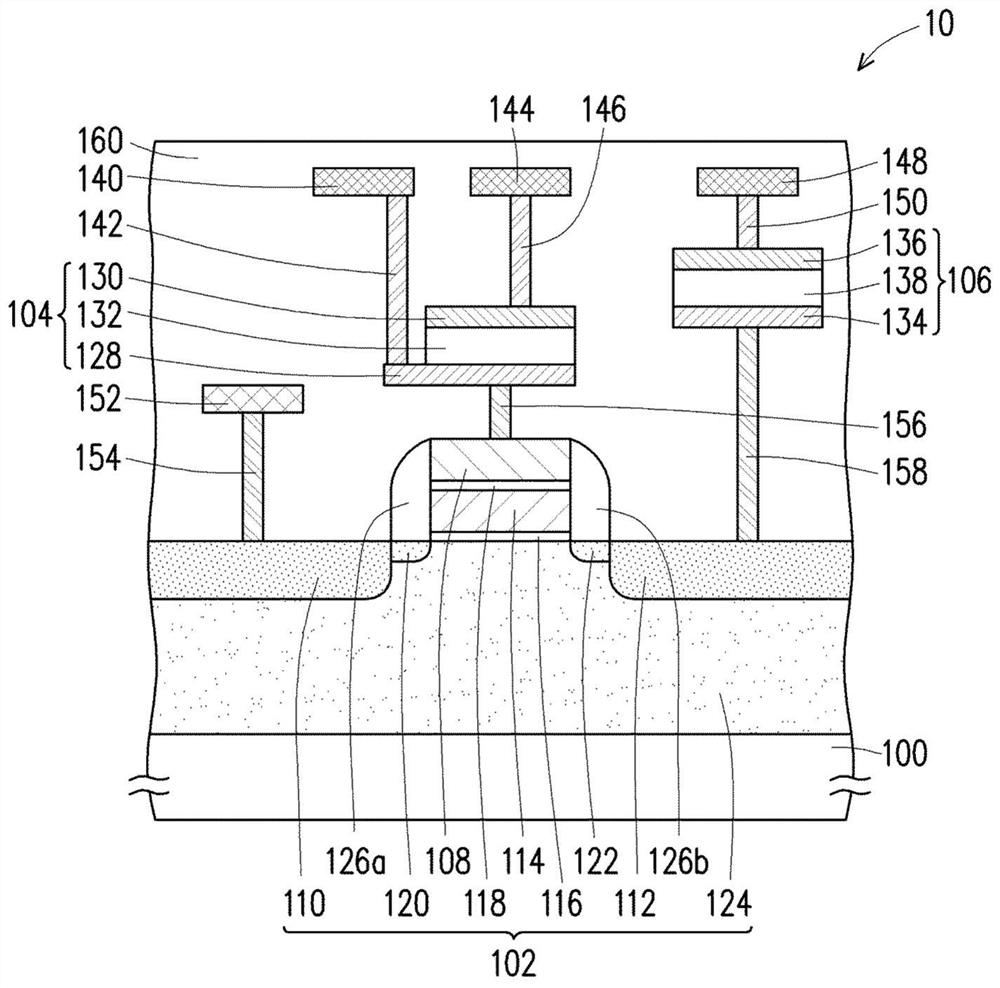

[0049] figure 1 It is a cross-sectional view of a composite memory structure according to an embodiment of the present invention. figure 2 is a cross-sectional view of a composite memory structure according to another embodiment of the present invention. image 3 is a cross-sectional view of a composite memory structure according to another embodiment of the present invention.

[0050] Please refer to figure 1 The composite memory structure 10 includes a substrate 100 , a flash memory 102 , a resistive random access memory 104 and a resistive random access memory 106 . The flash memory 102 is located on the substrate 100 . The substrate 100 may be a semiconductor substrate, such as a silicon substrate. In addition, in the circuit, the flash memory 102 , the RRAM 104 and the RRAM 106 can be three resistors connected in series. In some embodiments, the flash memory 102 , the RRAM 104 and the RRAM 106 may have the same resistance value.

[0051] The flash memory 102 includ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More