CML clock frequency dividing circuit, secondary clock frequency dividing circuit and analog-to-digital converter

A clock frequency division and frequency division circuit technology, applied in the direction of analog-to-digital converter, analog/digital conversion, code conversion, etc., can solve the problem of high power consumption of CML clock frequency division circuit, achieve obvious power consumption reduction and speed up operation , the effect of reducing the level conversion time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

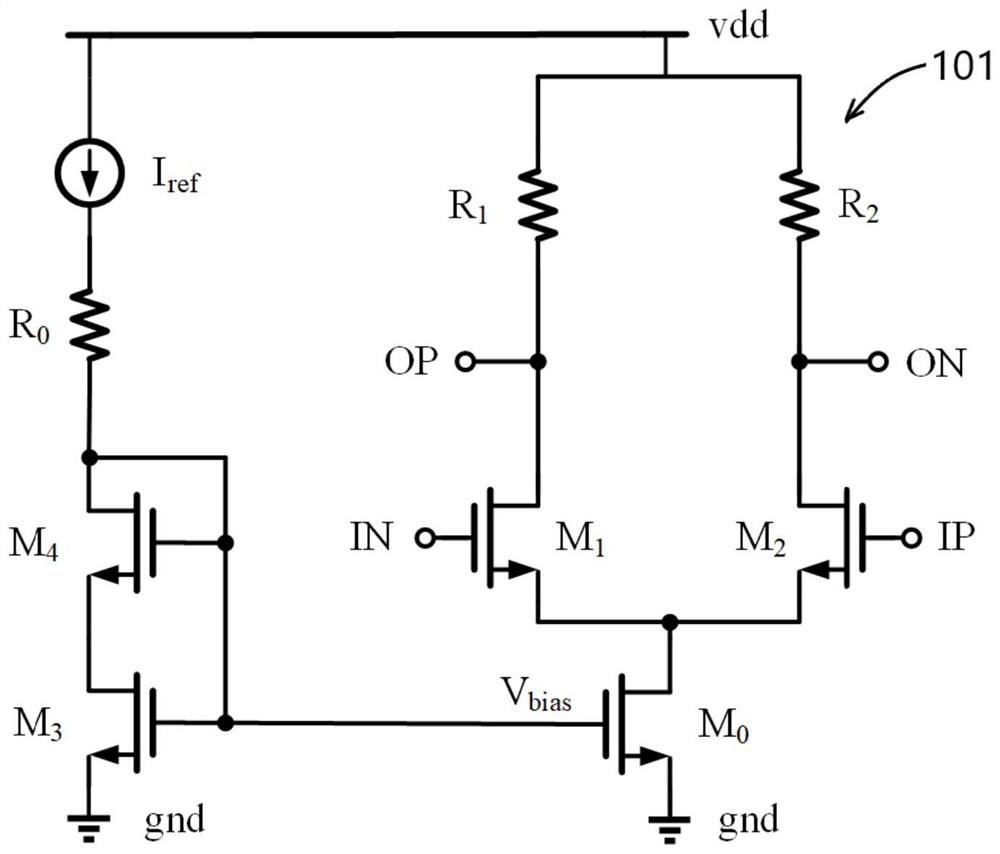

[0047] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are part of the embodiments of the present invention, not all of them.

[0048] Based on the embodiments of the present invention, those skilled in the art can make some simple modifications and embellishments without creative work, and all other obtained embodiments belong to the protection scope of the present invention.

[0049] Reference in the present invention to an "example" means that a particular feature, structure, or characteristic described in connection with the example can be included in at least one embodiment of the present invention. The presentation of this phrase in various places in the specification are not necessarily all referring to the same embodiment, nor are independent or alternative embodiments mutuall...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More