Market low-delay interface device based on FPGA (Field Programmable Gate Array)

An interface device and low-latency technology, which is applied in the field of low-latency interface devices, can solve problems such as huge system overhead, and achieve the effects of reducing delay, reducing the number, and speeding up data output

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044] The present invention will be described in detail below in conjunction with the accompanying drawings and specific embodiments. Note that the aspects described below in conjunction with the drawings and specific embodiments are only exemplary, and should not be construed as limiting the protection scope of the present invention.

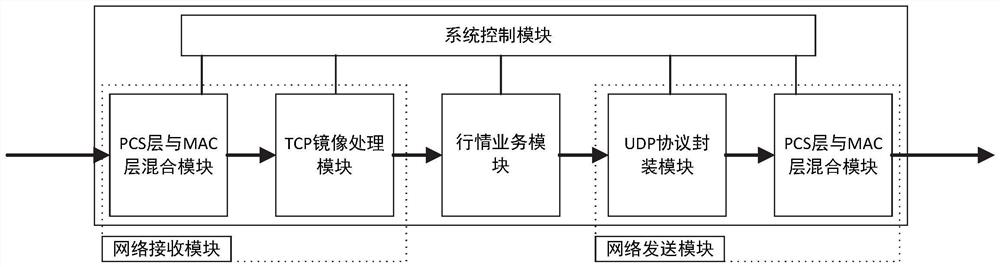

[0045] figure 1 The principle of an embodiment of the FPGA-based market low-latency interface device of the present invention is shown. See figure 1 , the device in this embodiment includes: a network receiving module and a network sending module, a quotation business module, and a system control module.

[0046] The network receiving module receives the input from the external network, and transmits the received data to the quotation business module after processing.

[0047] The network sending module receives the output of the quotation business module, and transmits the received data to the external network after processing.

[0048] T...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More