IRDrop simulation method for large-scale array circuit

A simulation method and large-scale technology, applied in electrical digital data processing, special data processing applications, instruments, etc., which can solve the problems of large differences in circuit IRDrop simulation results and uneven parasitic resistance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

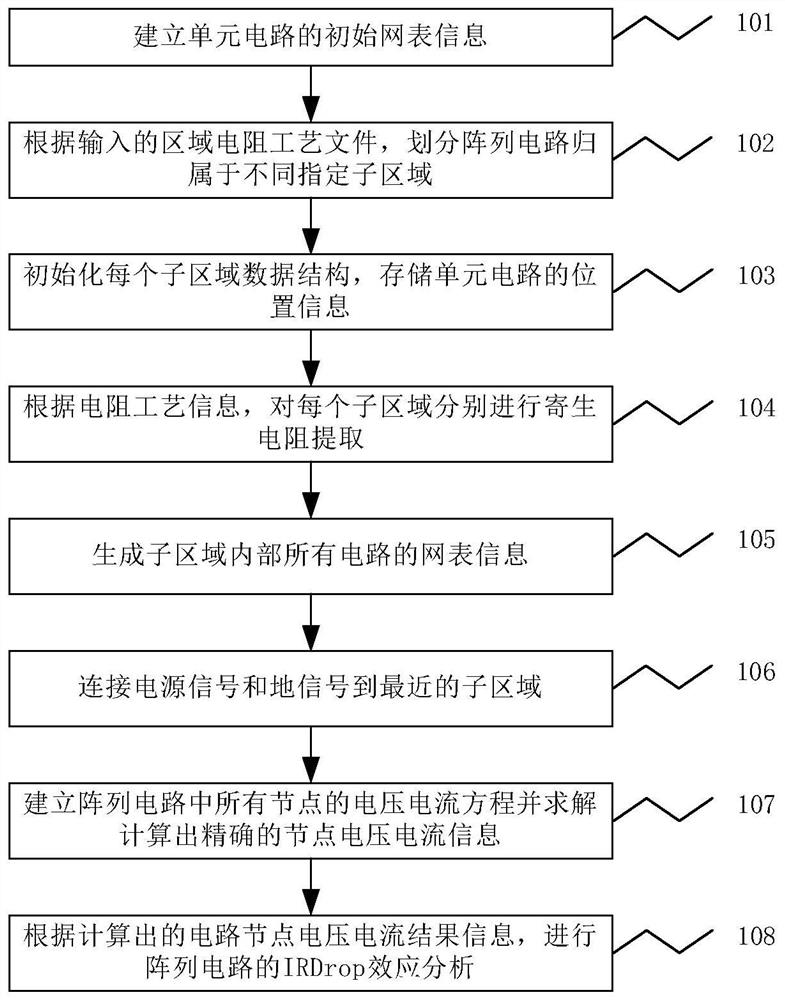

[0029] figure 1 For the flow chart of the IRDrop simulation method according to the large-scale array circuit of the present invention, reference will be made below figure 1 , the IRDrop simulation method of the large-scale array circuit of the present invention is described in detail.

[0030] First, in step 101, the initial netlist information unit netlist of the unit circuit Unit is established.

[0031] In the embodiment of the present invention, the netlist information includes: all unit circuit port node information, all unit circuit internal node information, all resistance information connected to different nodes, and all active device information.

[0032] In step 102, according to the input area resistance process file, the array circuits are divided into different specified sub-areas.

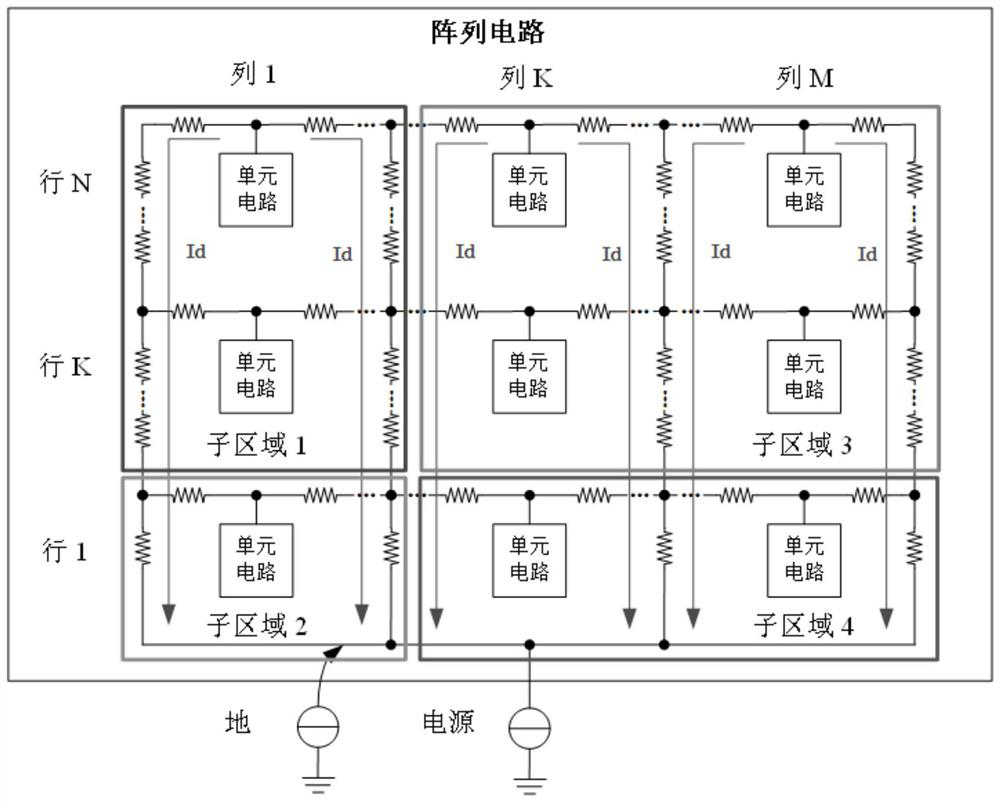

[0033] In the embodiment of the present invention, the sub-regions are numbered after dividing the array circuit into different specified sub-regions, as in figure 2 As shown, th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More