Clock circuit and memory

A clock circuit and clock technology, applied in static memory, digital memory information, logic circuits, etc., can solve the problem of mismatch between the system clock signal and the data strobe clock signal, and achieve synchronization and handshake functions. small change effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

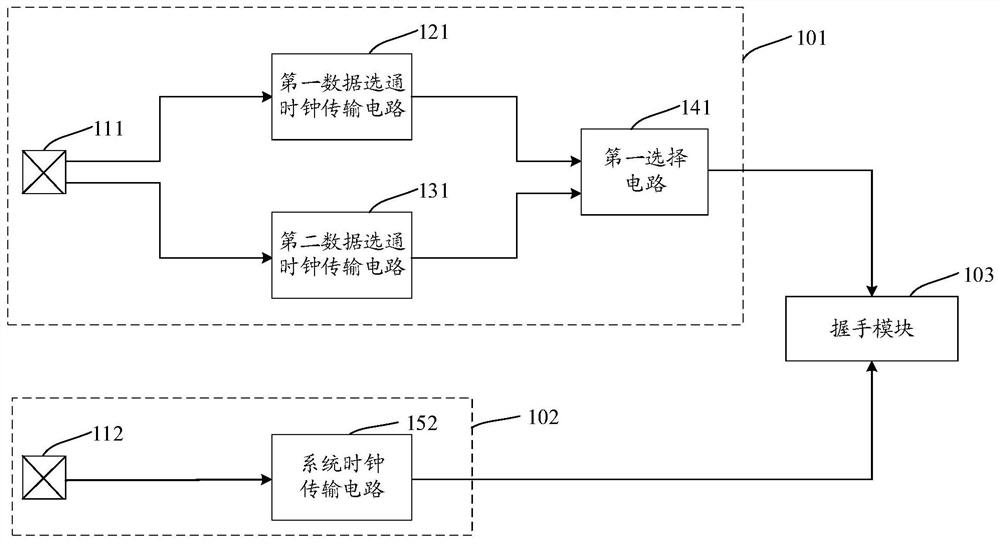

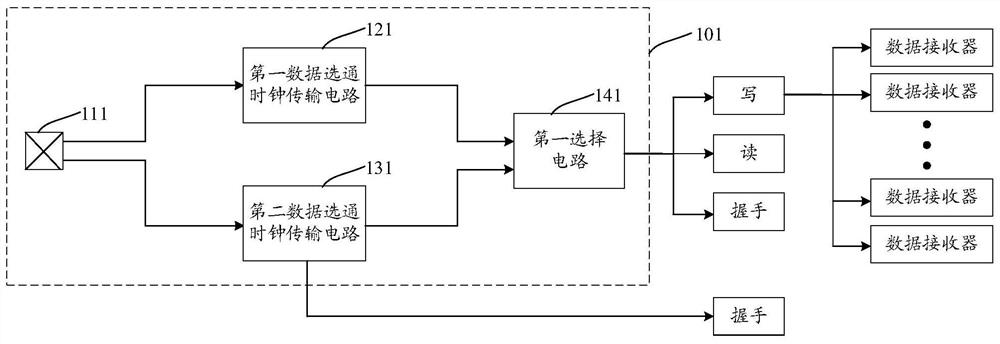

[0035] In order to alleviate the timing constraints of reading and writing of the memory, a WCK clock signal, that is, a data strobe clock signal, is introduced into the memory. In order to meet different performance requirements, the data transmission rate of the same memory can be fast or slow, and the transmission rate of the corresponding WCK clock signal can be a transmission rate exceeding a preset value, or a transmission rate lower than a preset value. For example, when the data transmission rate exceeds 3200Mbps, a current mode logic (CML, Current ModeLogic) frequency divider can be introduced to reduce the interference on the WCK clock signal; when the data transmission rate is lower than 3200Mbps, a CMOS frequency divider can be used to Maximum power saving.

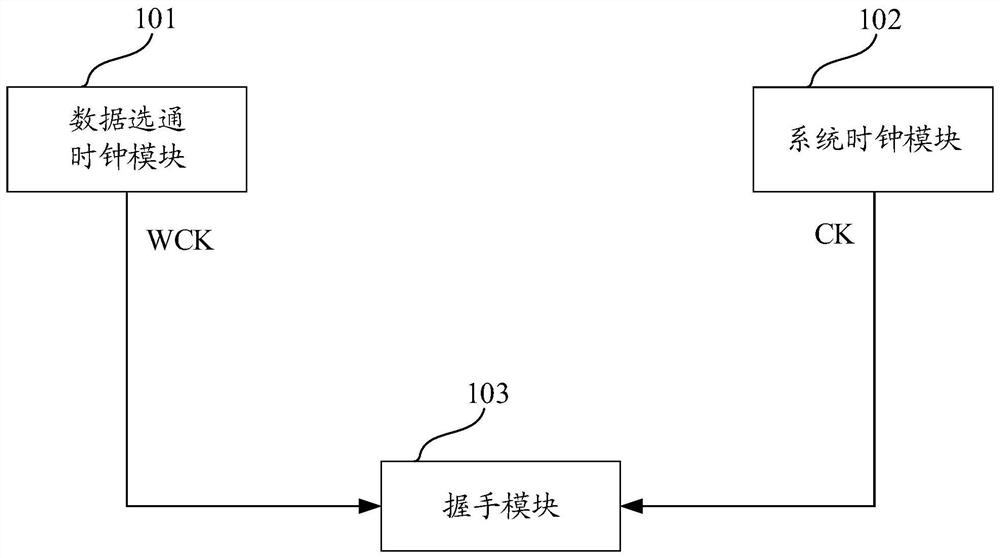

[0036] That is to say, if the transmission rate of the WCK clock signal in the memory is different, the WCK clock signal is transmitted through different transmission paths. There is also a CK clock signal (s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More