Memory controller and chip product

A technology of memory controller and memory, which is applied in the direction of program control design, instruments, generation/distribution of signals, etc., and can solve the problems of increased delay in dispatching commands and transmission data

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

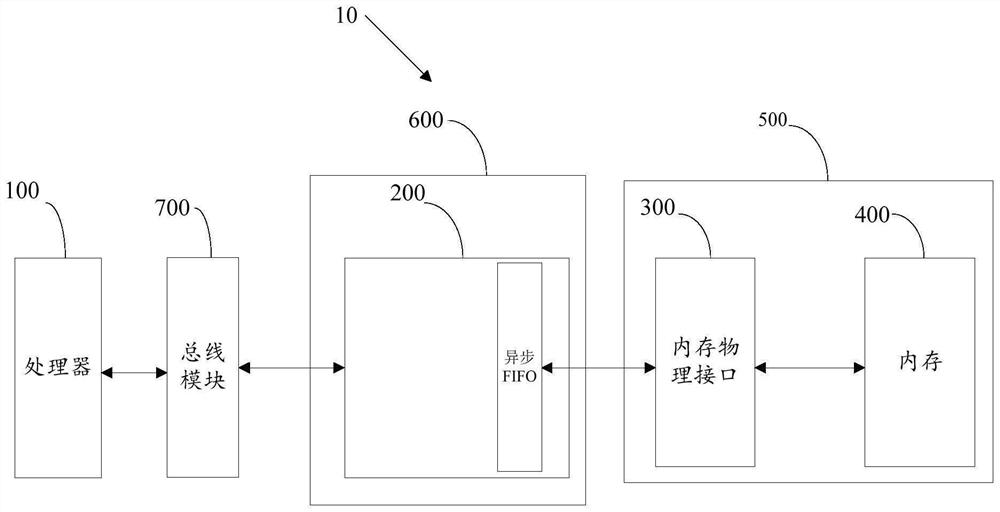

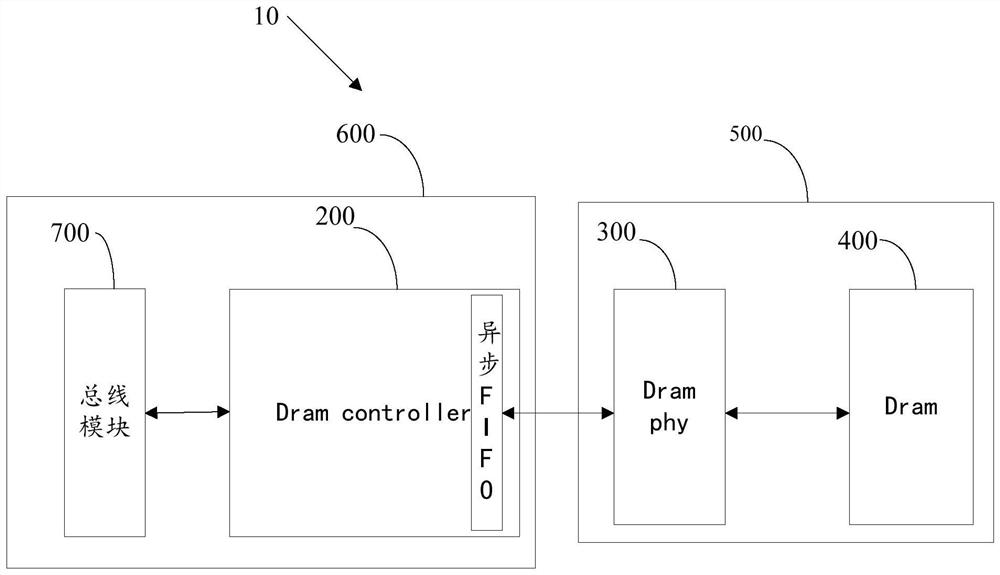

[0030] The technical solutions in the embodiments of the present application will be described below with reference to the drawings in the embodiments of the present application.

[0031] It should be noted that like numerals and letters denote similar items in the following figures, therefore, once an item is defined in one figure, it does not require further definition and explanation in subsequent figures. Meanwhile, in the description of the present application, the terms "first", "second" and the like are only used to distinguish descriptions, and cannot be understood as indicating or implying relative importance.

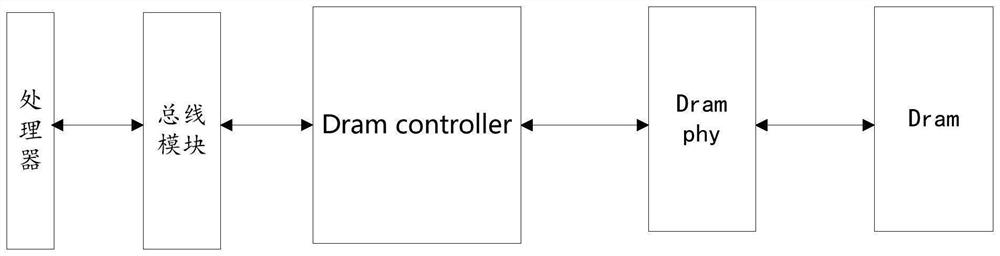

[0032] Dram: refers to dynamic random access memory.

[0033] Dram controller: Complete Dram memory read and write operations and scheduling, so that the read and write operations meet the relevant protocols, and complete data transmission.

[0034] Dram PHY: Change the scheduling command of the Dram controller into control signals and data signals that meet ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More