Automatic script compiling and using method for solving physical design long-line time sequence delay

A technology for automated scripting and physical design, applied in the semiconductor field, it can solve problems such as manual optimization, large workload, and prolonged design cycle, and achieve the effect of reducing delay, reducing line delay, and clear and definite variables

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0071] The present invention will be further described below in conjunction with the accompanying drawings and embodiments.

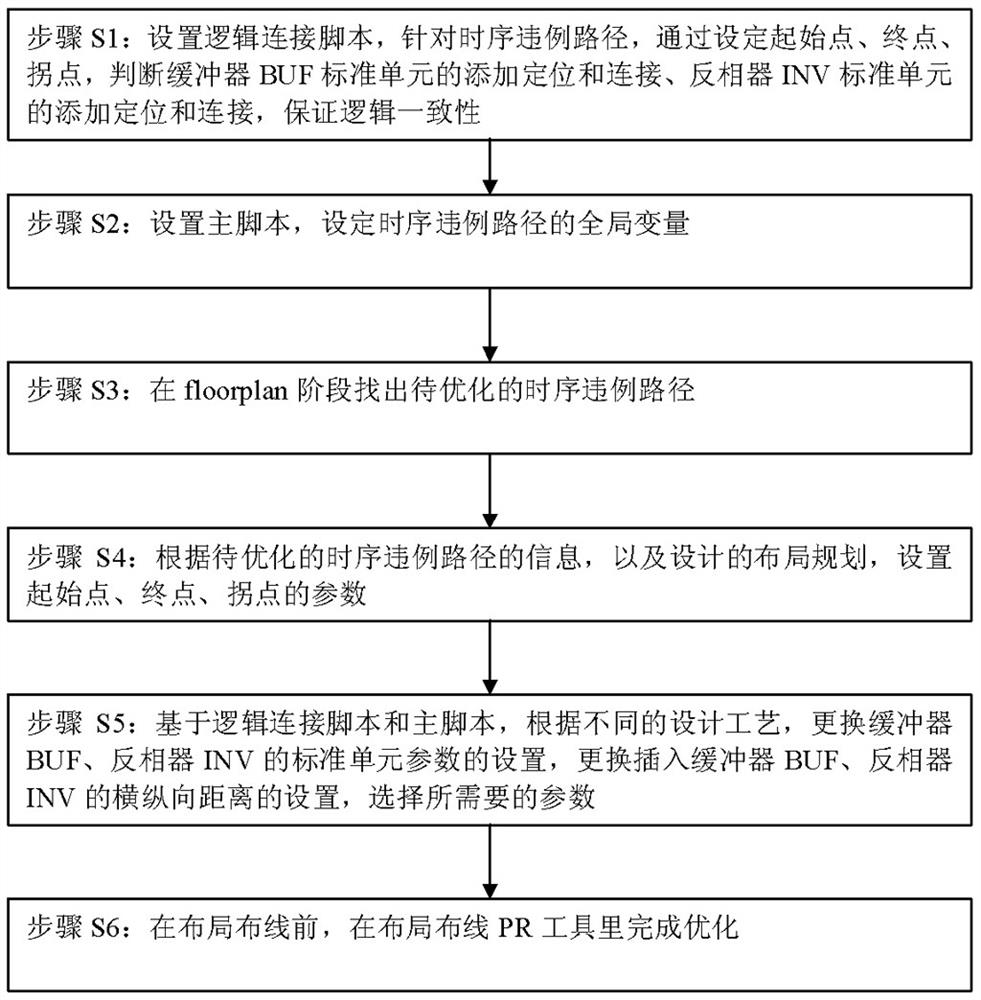

[0072] like figure 1 As shown in the figure, an automatic script writing and using method for solving the long-term timing delay of physical design, including the following steps:

[0073] Step S1: Set up the logic connection script, for the timing violation path, by setting the start point, end point, and inflection point, determine the addition location and connection of the buffer BUF standard cell, and the addition location and connection of the inverter INV standard cell to ensure the logic consistency sex.

[0074] The optimization logic of the logical connection script for the line path that needs to be optimized is to find the coordinates of the starting point and the end point connected by this line, and calculate according to the coordinate value; first determine the direction of the line, up, down, left, and right, and then calculate accordi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com