Integrated circuit concurrent test device and method

A testing device and integrated circuit technology, which is applied in electronic circuit testing, measuring devices, measuring electricity, etc., can solve the problems of multi-time, low testing efficiency, and inability to accurately synchronize the measured signals, and achieve the effect of reducing difficulty and improving efficiency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

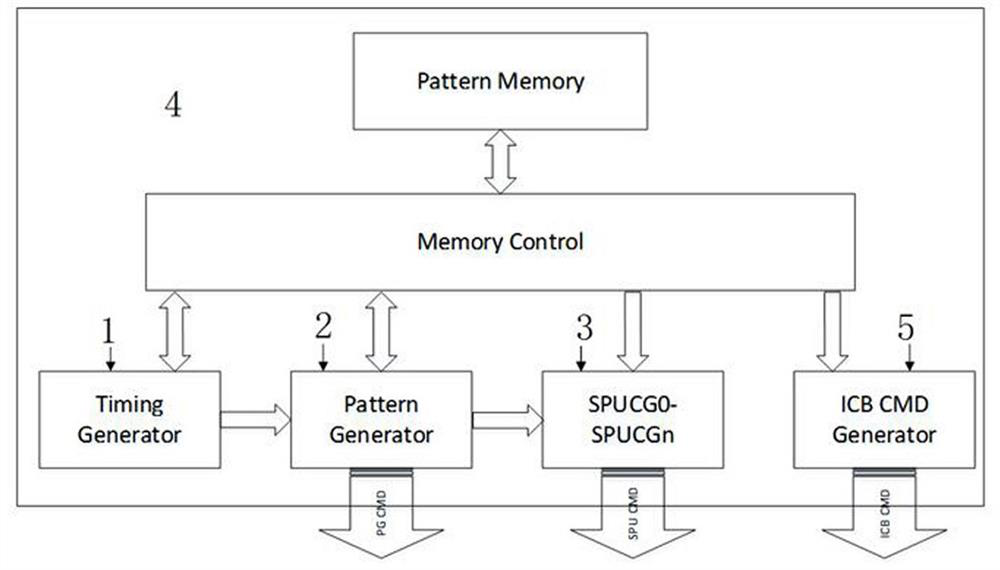

[0034] The instrument control bus command generator ICMG5 (ICM Generator, ICMG) is used for the instrument control command ICO (InstrumentControl Opcodes, referred to as ICO, specific reference image 3 Description) is transformed into an instrument control message ICM (Instruments Control Message, ICM for short). Through the instrument control bus ICB, it is transmitted to the parameter test controller PTC of each channel, so that the test processor completes the test control of each non-digital channel.

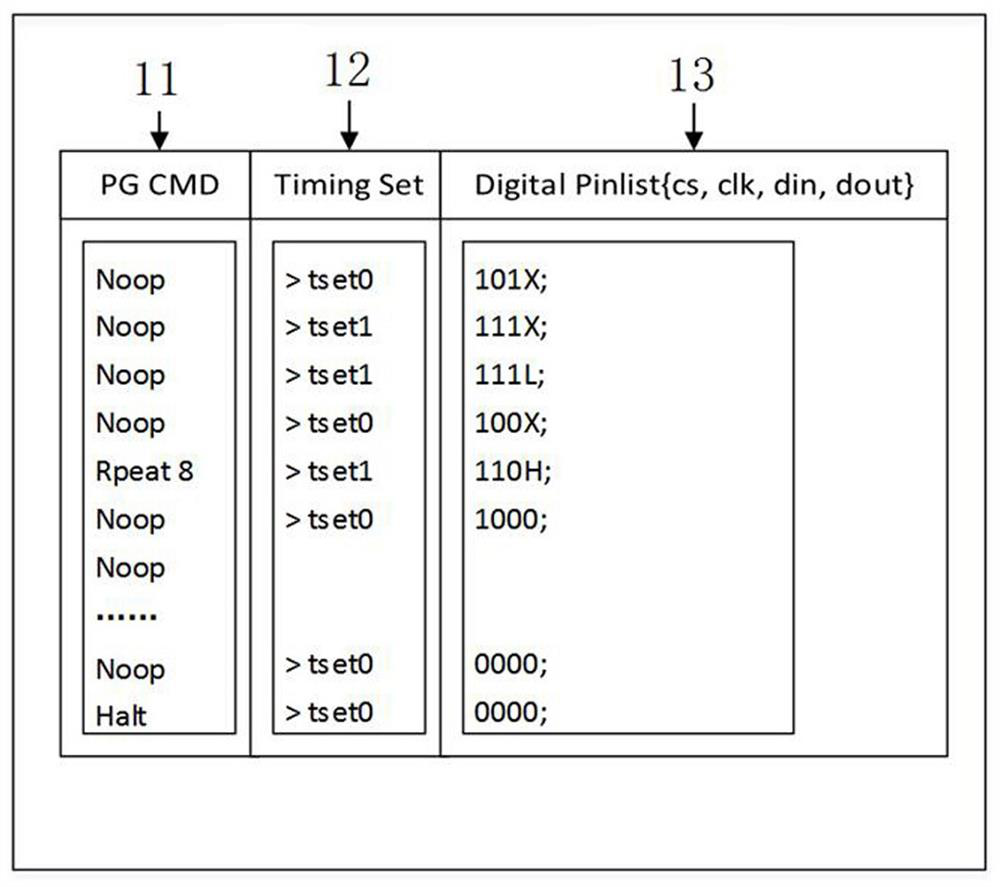

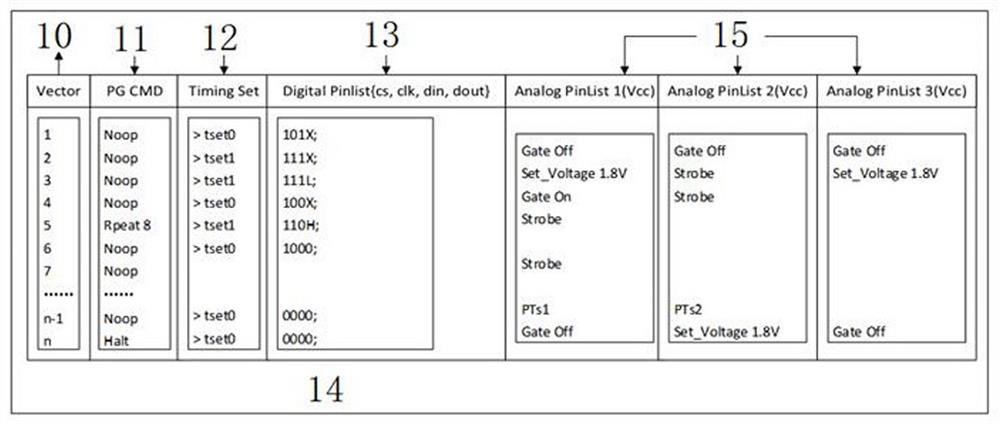

[0035] like figure 2 As shown, it is a Pattern file processed by a traditional test processor. The Pattern file processed by a traditional test processor is composed of a test pattern generator control command 11, a timing setting 12, and a digital channel list 13, providing the pattern test generator. all the information for .

[0036] Test pattern generator control command 11 (Pattern GeneratorCommand), which generates the control timing required for pattern testing, i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More