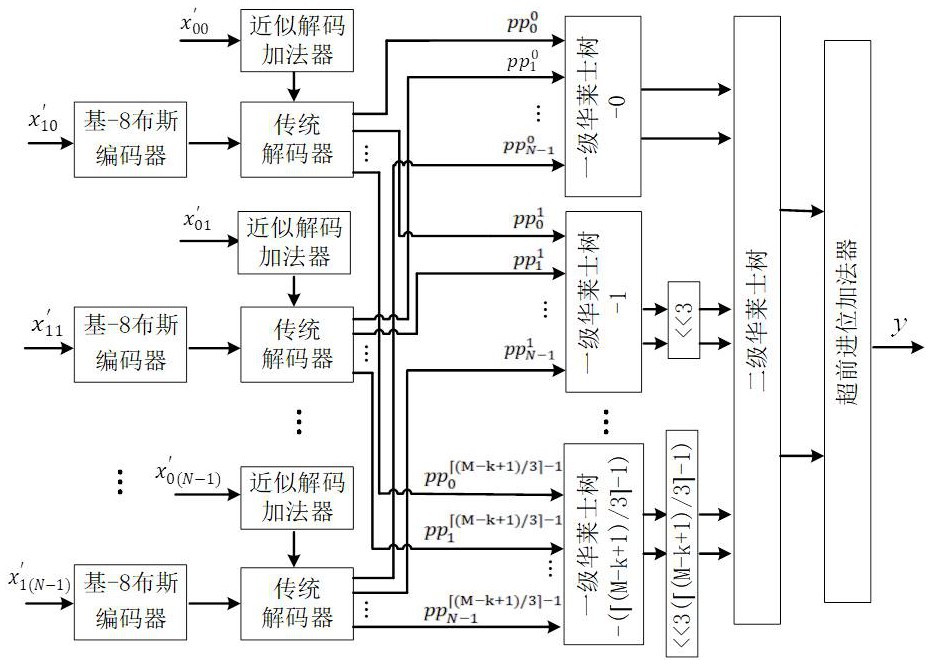

Low-energy-consumption high-precision approximate parallel fixed-width multiplication and accumulation device

A multiplication-accumulation and high-precision technology, which is applied in the field of low-power consumption and high-precision approximate fixed-width multiplication-accumulation devices, can solve the problems of failing to achieve an effective balance between precision and hardware, rough approximation methods, etc., and shorten the length of the critical path and reduce the number of circuits. Complexity, the effect of increasing parallelism

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

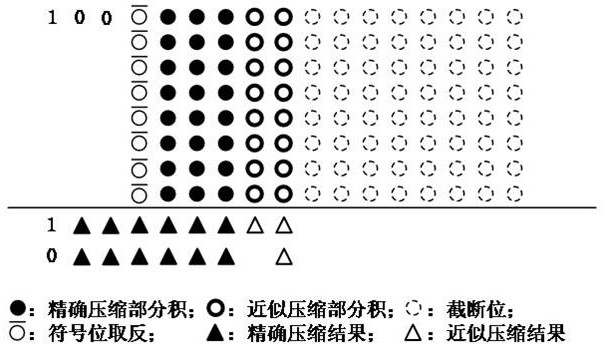

[0049] The approximate 4_2 compressor formula used in a one-stage partial product compression circuit is: , ; Precise adders include precise full adders and precise half adders. The sign compensation bit of the partial product of each row is not included in the compression tree, and the error is reduced by the constant compensation method.

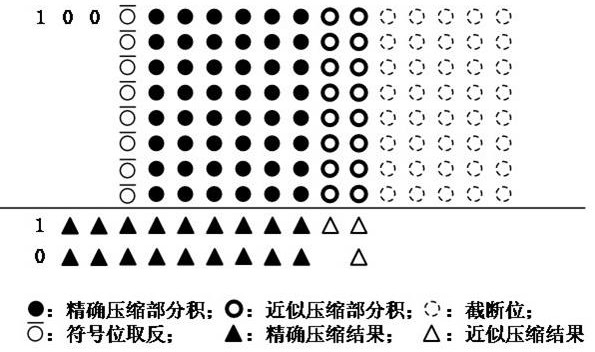

[0050] As a further optimization scheme of this embodiment, the two-level partial product compression circuit performs unified processing on the sign bit when the input symbol is determined: on the premise that only the value bits are reserved, the lowest bit compression tree of the first-level partial product compressor Add "111" to the high bit of any output, and add "110" to the high bit of any output of the second-lowest and second-highest compression trees, such as image 3 shown.

[0051] As a further optimization scheme of this embodiment, the second-level partial product compressor includes a constant compensation part for tru...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More