Automatic control method and system for low-power-consumption mode of chip

A technology of automatic control system and low power consumption mode, which is applied in the fields of instruments, computing, electrical digital data processing, etc. It can solve the problems of huge delay loop area, difficult traceability, different clock control, etc. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] The present invention will be described in detail below with reference to the accompanying drawings and specific embodiments. The present invention is not limited to this embodiment, and other embodiments may belong to the scope of the present invention as long as it conforms to the gist of the present invention.

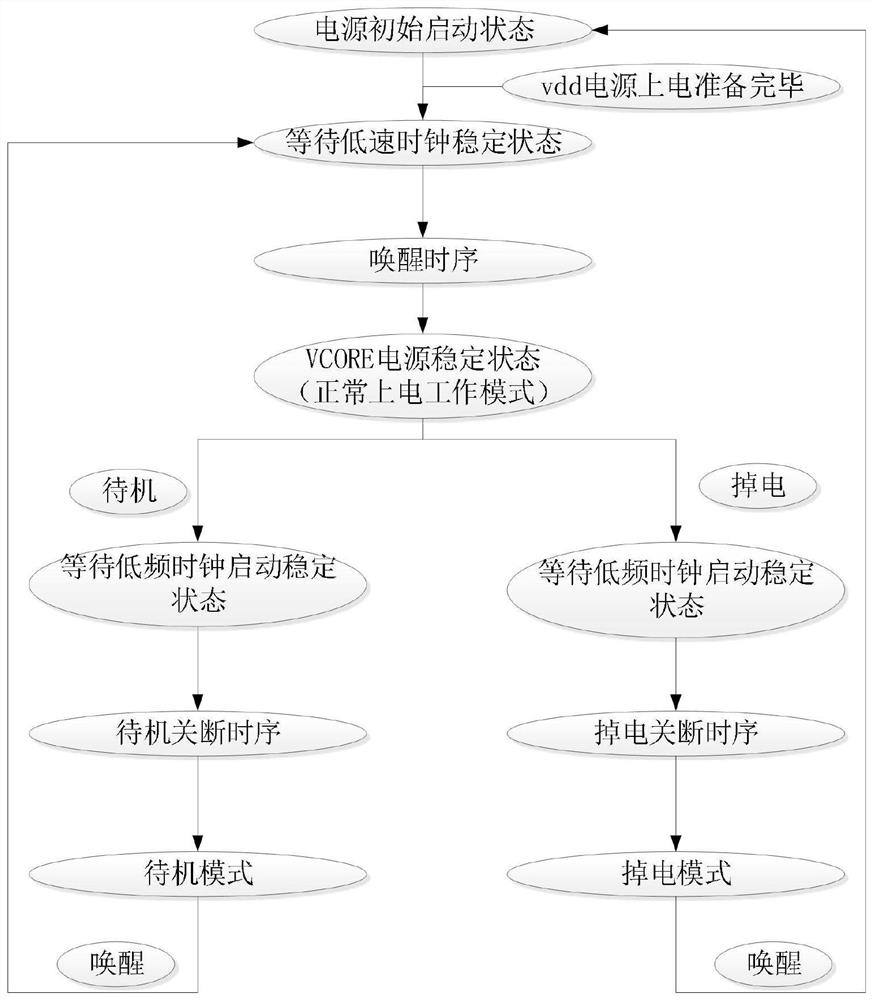

[0034] In a preferred embodiment of the present invention, based on the above-mentioned problems existing in the prior art, an automatic control method for a low power consumption mode of a chip is provided. The chip has a plurality of power supply partitions, and each power supply partition is powered by a power supply, The chip is configured with a power control module;

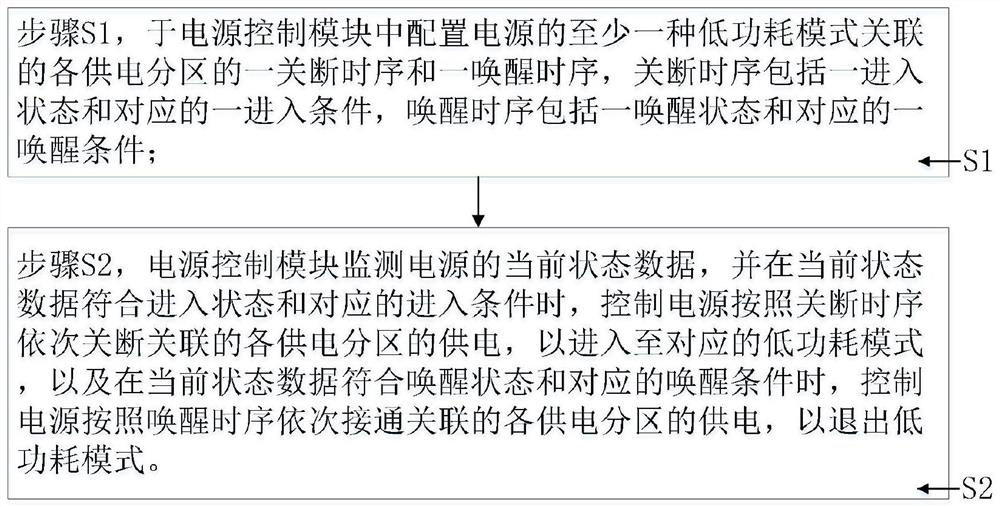

[0035] like figure 1 As shown, the automatic control method of the low power consumption mode includes:

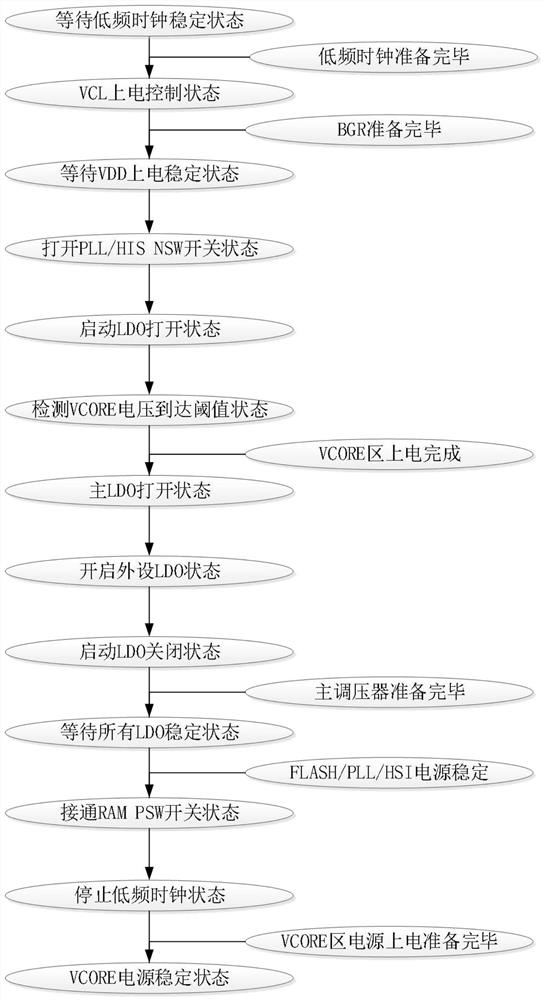

[0036] Step S1, in the power control module, configure a shutdown sequence and a wake-up sequence of each power supply partition associated with at least one low-power mode of the po...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com