Three-dimensional chip layout method and device and terminal equipment

A three-dimensional chip and layout method technology, applied in the computer field, can solve the problems of low layout accuracy and increase power consumption of three-dimensional chips, and achieve the effects of improving layout accuracy, prolonging service life and reducing power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

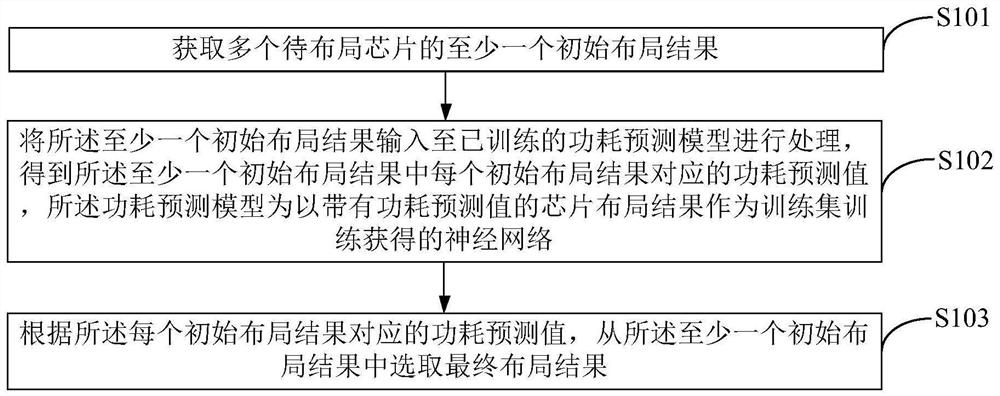

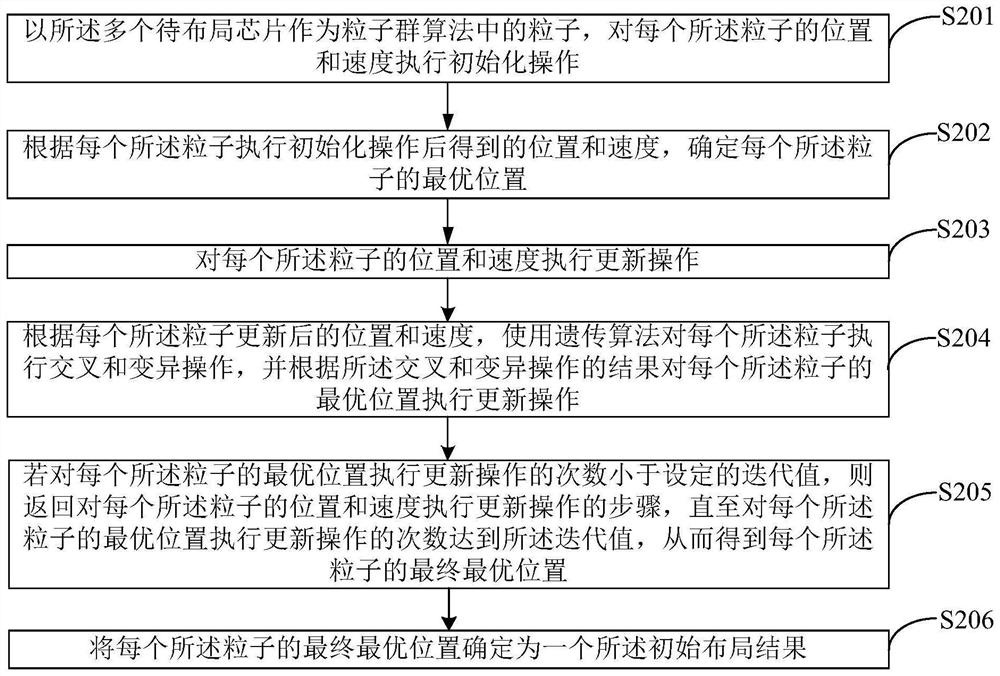

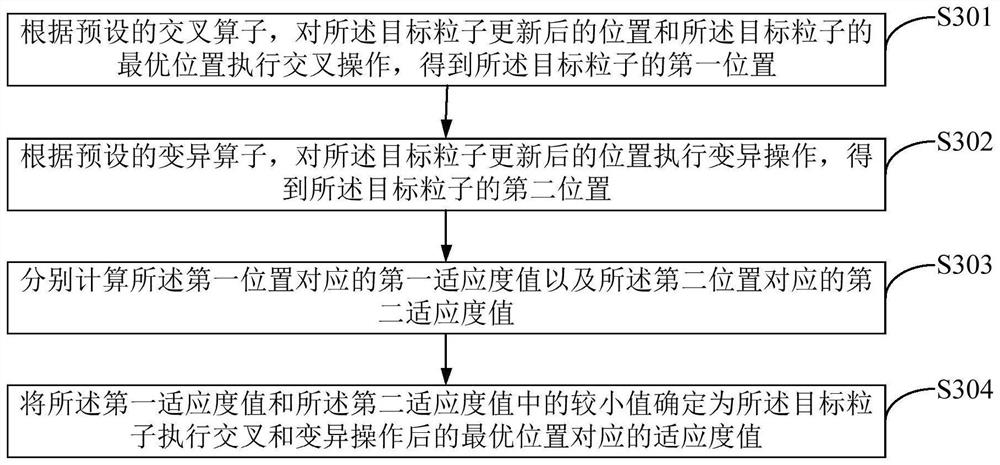

Method used

Image

Examples

Embodiment Construction

[0052] In the following description, for the purpose of illustration rather than limitation, specific details, such as specific system structures and technologies, are provided for a thorough understanding of the embodiments of the present application. However, it will be apparent to those skilled in the art that the present application may be practiced in other embodiments without these specific details. In other instances, detailed descriptions of well-known systems, devices, circuits, and methods are omitted so as not to obscure the description of the present application with unnecessary detail.

[0053] It is to be understood that, when used in this specification and the appended claims, the term "comprising" indicates the presence of the described feature, integer, step, operation, element and / or component, but does not exclude one or more other The presence or addition of features, integers, steps, operations, elements, components and / or sets thereof.

[0054] It will a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More