SLT test method and system of SIP chip

A testing method and testing system technology, applied in electronic circuit testing, measuring devices, measuring electrical variables, etc., can solve the problems of error-prone and complicated operation process, and achieve the effect of convenient tracking and positioning, improving testing flexibility and testing efficiency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

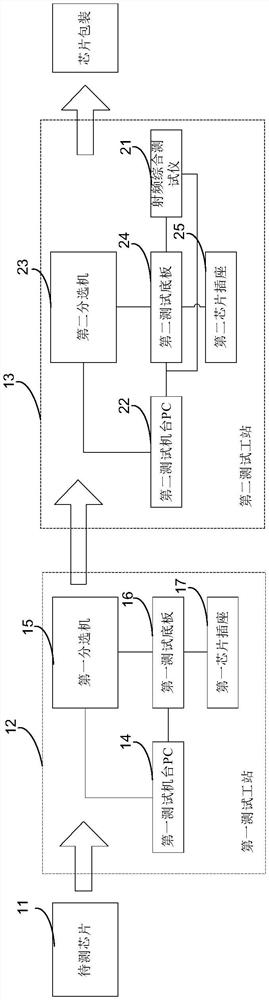

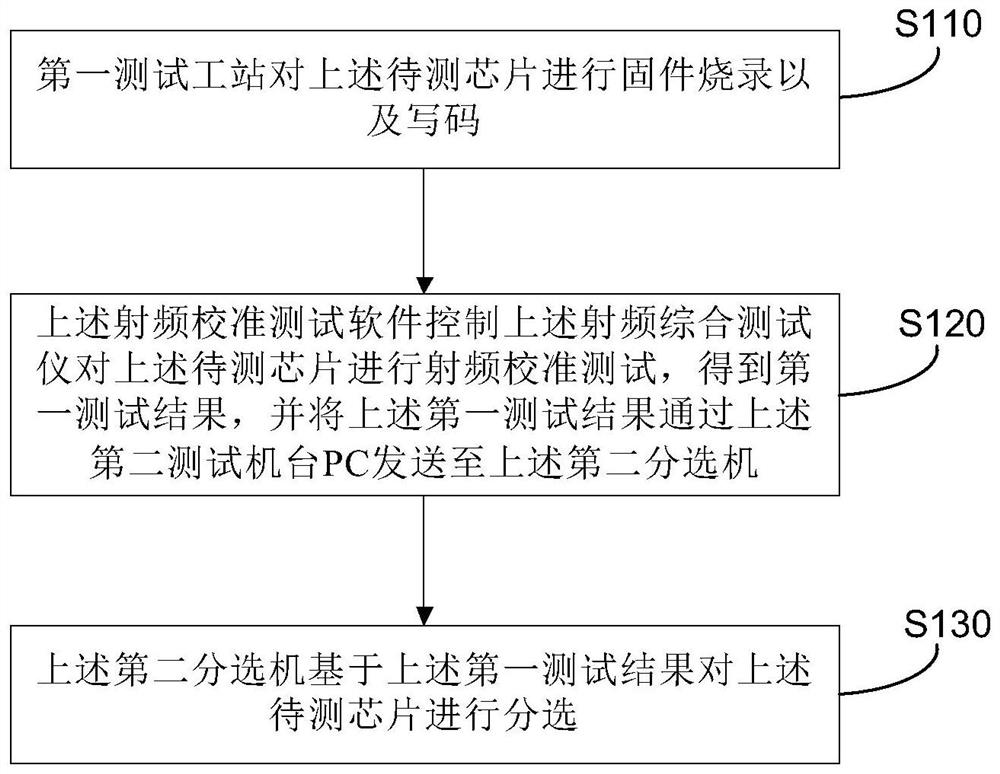

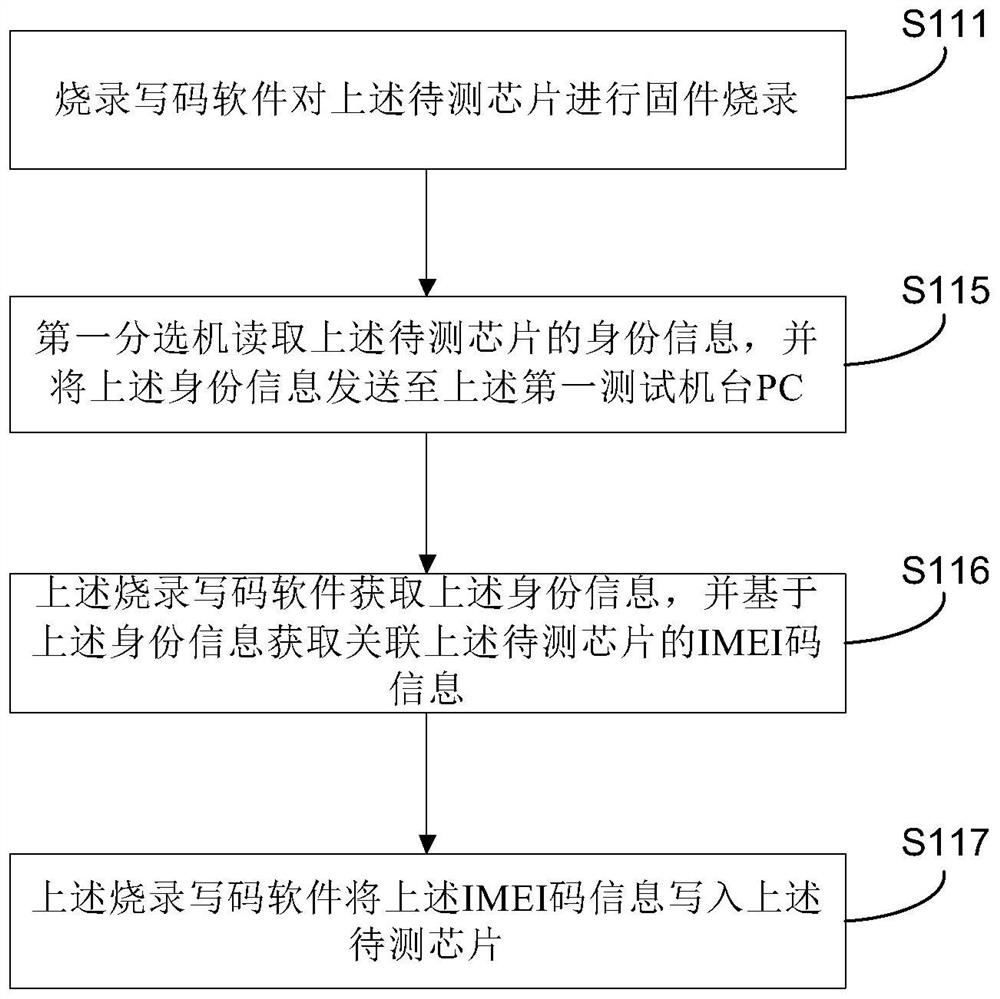

[0050] Example embodiments will now be described more fully with reference to the accompanying drawings. However, example embodiments can be embodied in various forms and should not be construed as limited to the embodiments set forth herein. Rather, these embodiments are provided so that this disclosure will be thorough and complete, and will fully convey the concept of example embodiments to those skilled in the art. The described features, structures, or characteristics may be combined in any suitable manner in one or more embodiments. In the following description, numerous specific details are provided in order to give a thorough understanding of the embodiments of the present disclosure. However, one skilled in the art will appreciate that the technical solutions of the present disclosure may be practiced without one or more of the specific details, or other methods, materials, devices, etc. may be employed. In other instances, well-known solutions have not been shown o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More