Method for producing metal layer virtual pattern

A technology of virtual patterns and metal layers, which is applied in the fields of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., and can solve problems such as metal wiring load effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

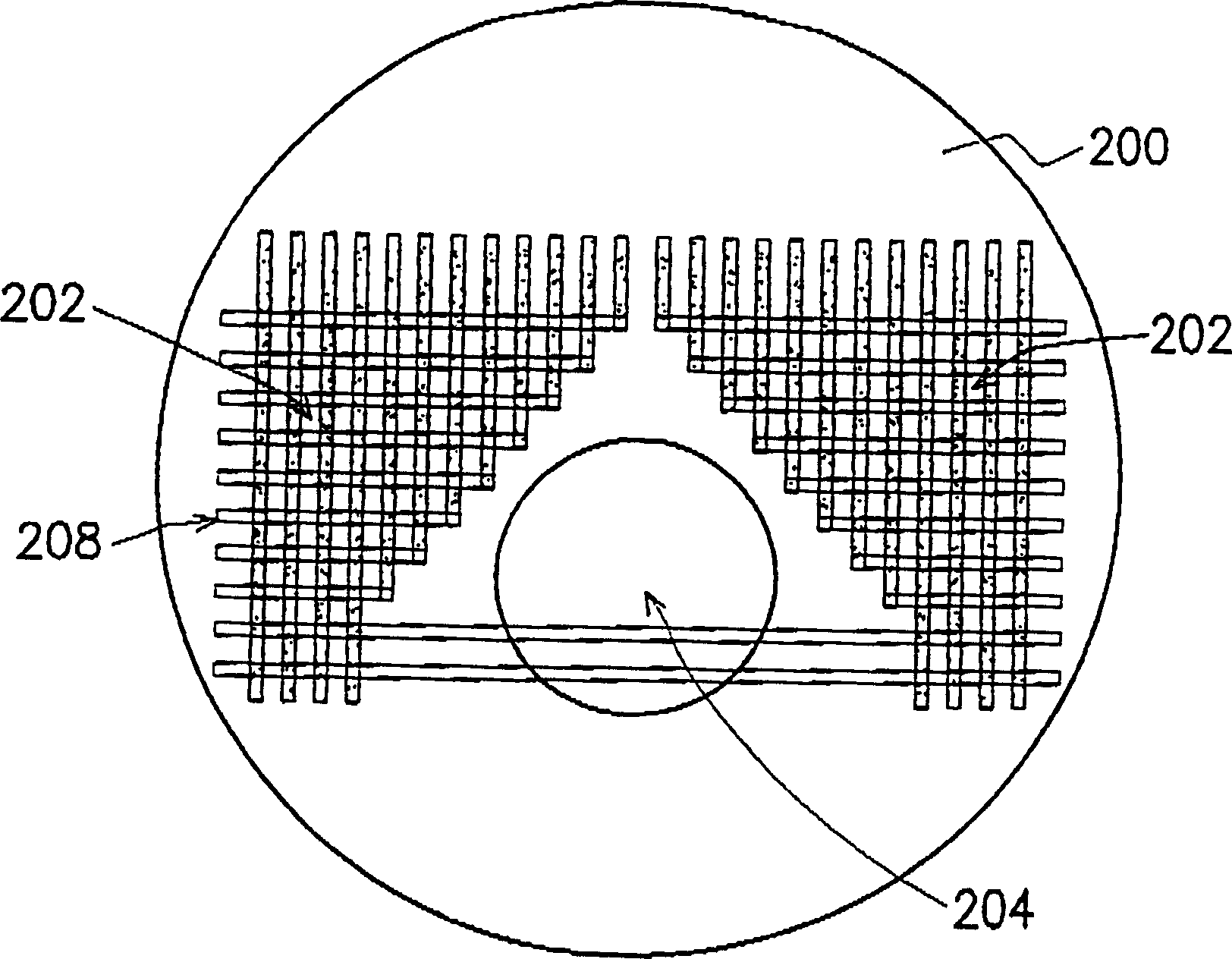

[0030] Figure 2A 2B is a schematic diagram of a design method with a metal layer dummy pattern according to a first preferred embodiment of the present invention, Figure 2A 2B is a top view of a silicon chip.

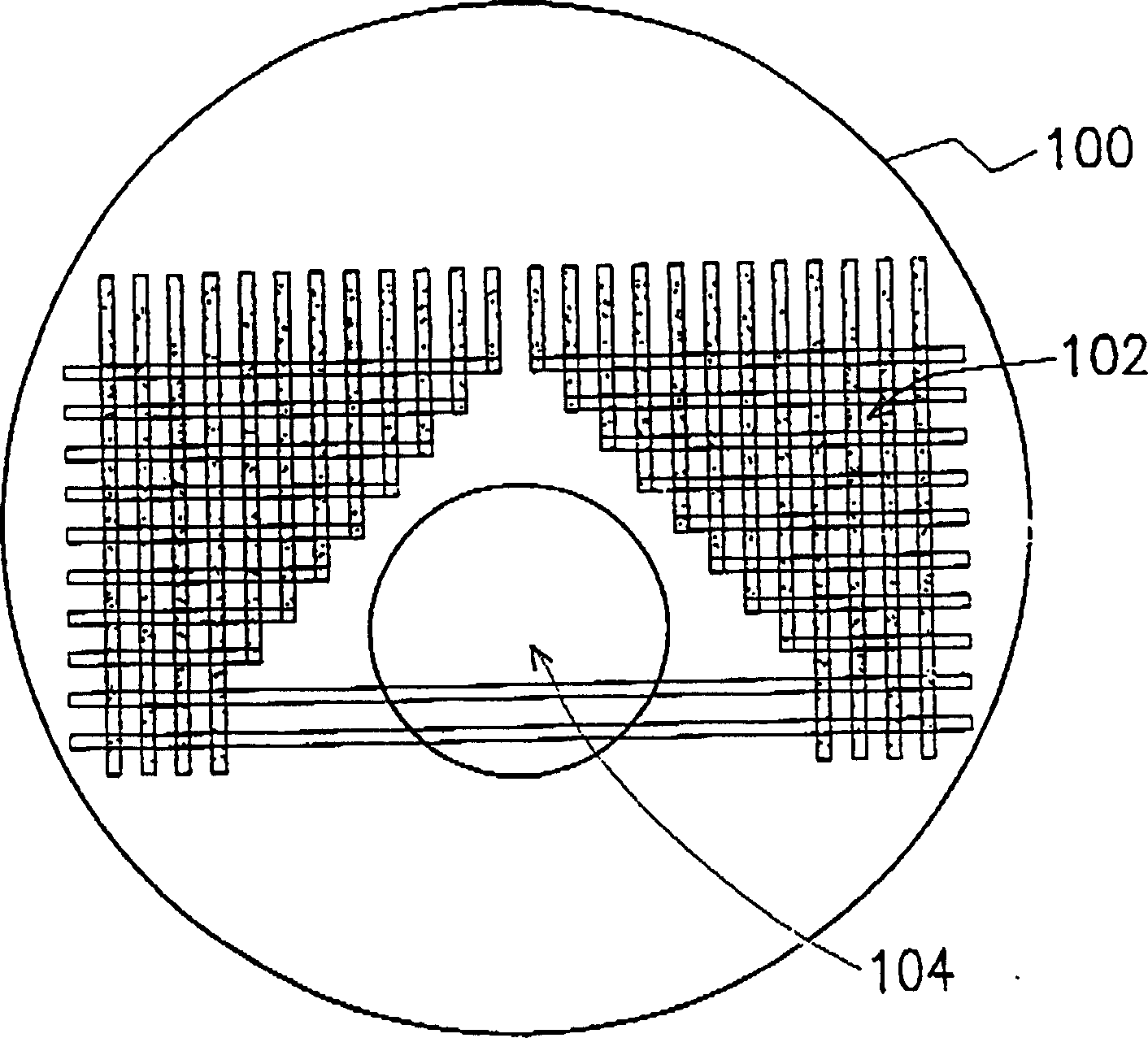

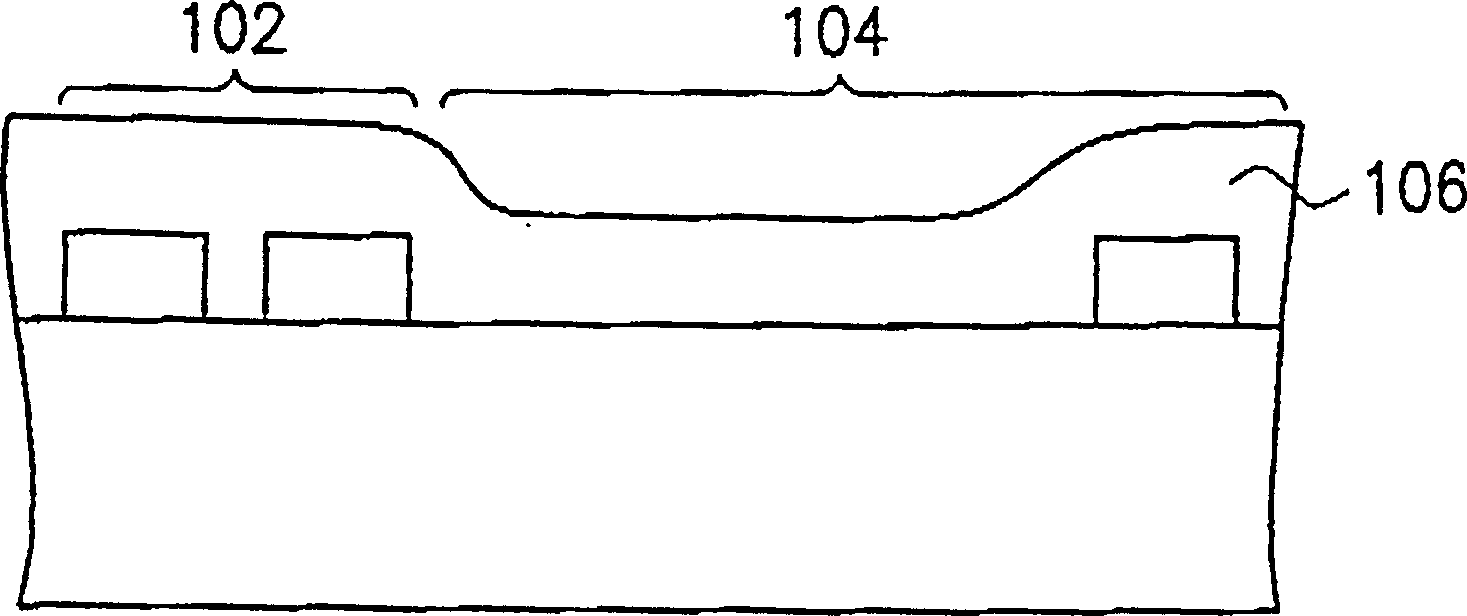

[0031] Please refer to Figure 2A Firstly, a semiconductor substrate 200 is provided. The substrate 200 includes a metal layer pattern dense area 202 and a metal layer pattern sparse area 204 . The metal layer pattern density of the metal layer pattern dense area 202 is higher than that of the metal layer pattern sparse area 204 . The metal layer pattern of the metal layer pattern dense area 202 includes, for example, a first metal layer pattern 206 with a first direction and uniform pattern density on the bottom layer, and a second metal layer pattern 206 with a uniform pattern density on the upper layer. The metal layer pattern 208, wherein the first direction is perpendicular to the second direction. In addition, the metal layer pattern in the metal layer patter...

no. 2 example

[0039] Figure 3A to Figure 3G A cross-sectional view of a process for generating a dummy pattern of a metal layer according to a second preferred embodiment of the present invention, wherein Figure 3F to Figure 3G The flow chart is presented in a top perspective view, Figure 3E for Figure 3F Section along the I-I tangent.

[0040] Please refer to Figure 3AA semiconductor silicon substrate 300 is provided, and a dielectric layer 302 and a metal layer 304 are sequentially formed on the substrate 300 . The material of the metal layer 304 is, for example, aluminum, copper, aluminum-copper alloy, or any other metal.

[0041] Please refer to Figure 3B The metal layer 304 is defined by typical photolithography and etching methods to form a plurality of metal lines 304a with a first direction, wherein the metal lines 304a have a uniform pattern density.

[0042] Next, according to the metal interconnection pattern to be formed, the connection between some unnecessary metal...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More