Grid structure and manufacture method as well as MOS part of grid structure

A gate structure and manufacturing method technology, applied in the field of metal oxide semiconductor transistors and their manufacturing, can solve the problems of reduced electrical characteristics of transistors, longer electron travel paths, and reduced element operation speed.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

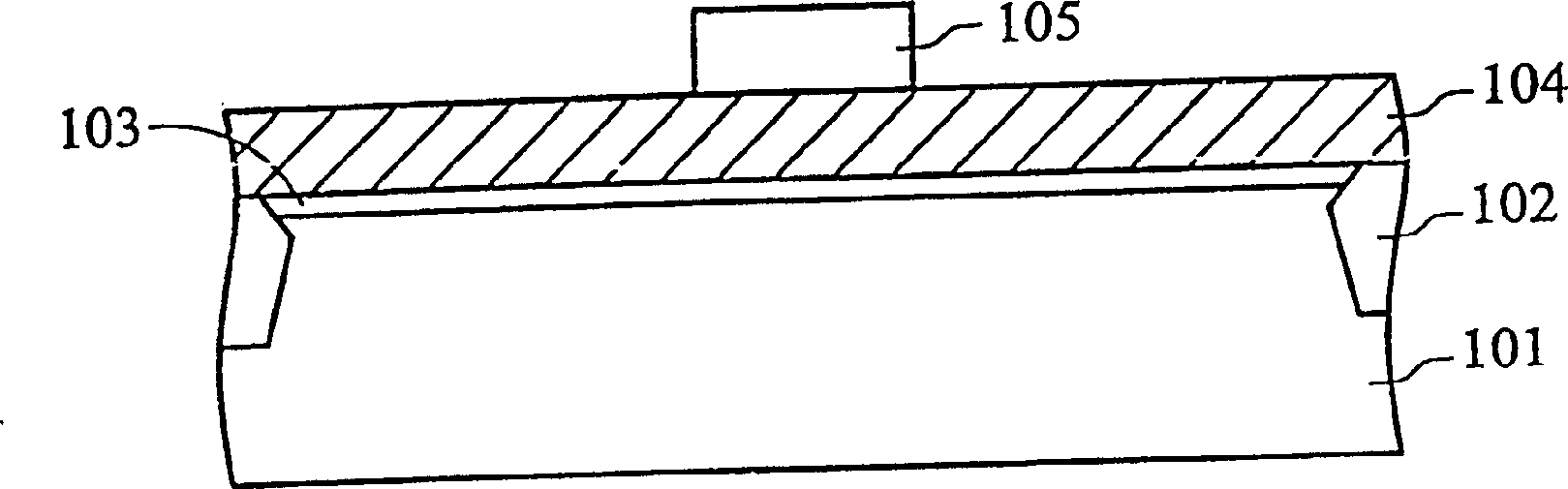

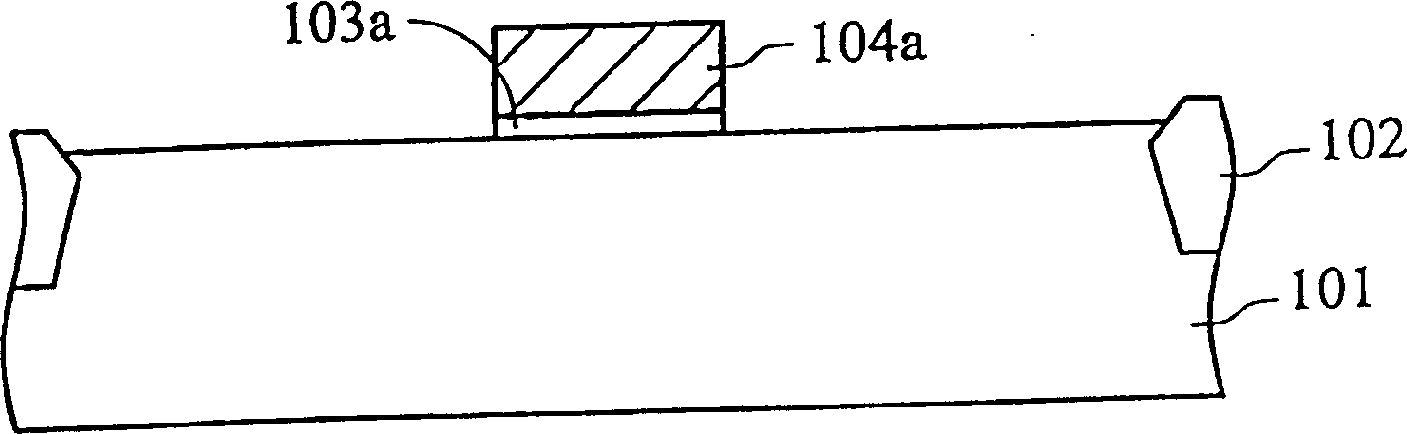

[0018] Figure 2a-2f Shown is a schematic flow chart of the steps of manufacturing the grid of the present invention.

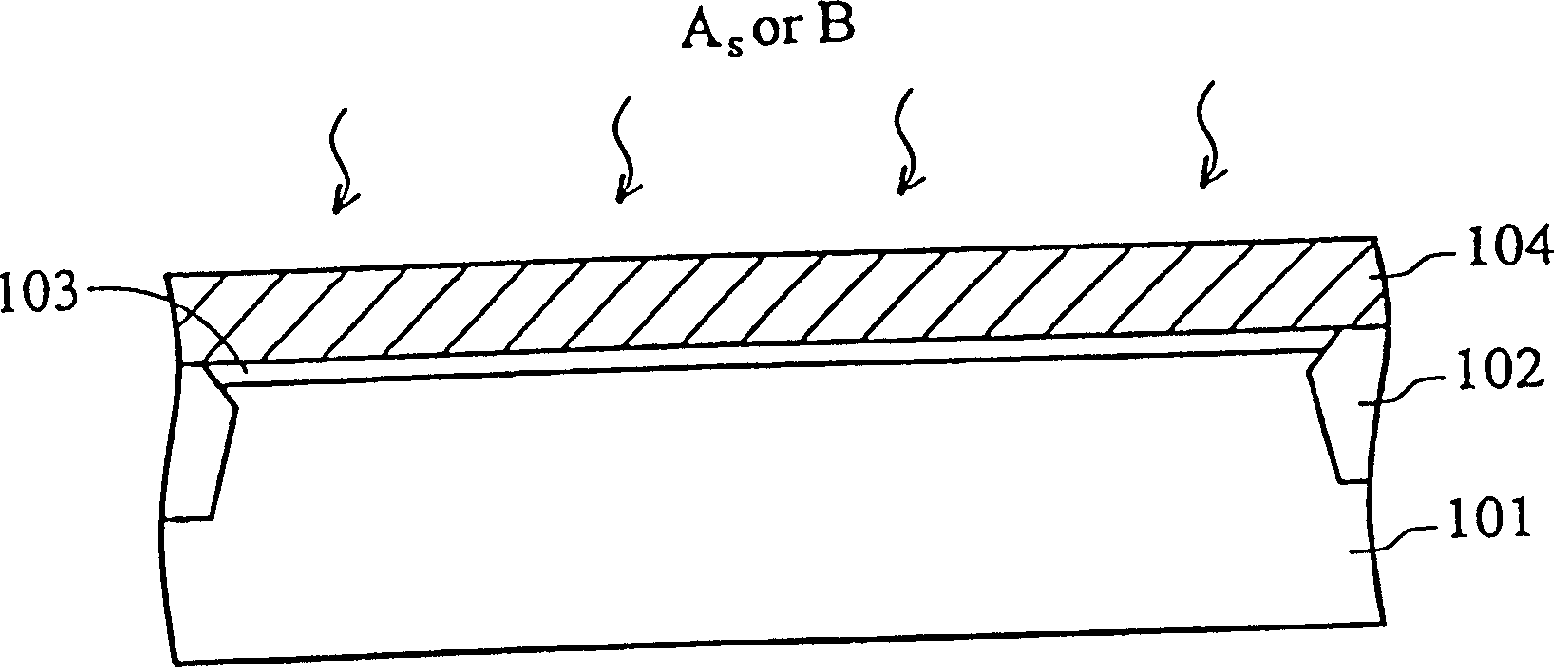

[0019] Please refer to Figure 2a Firstly, a semiconductor substrate 201 is provided, the semiconductor substrate 201 has an isolation region 202 , and the isolation region 202 is used to isolate an active region on the semiconductor substrate 201 . An oxide layer 203 is formed in the active region on the semiconductor substrate 201, and with hydrogen (H 2 ) and silane (SiH 4 ) in a processing chamber to perform a deposition step on the semiconductor substrate 201 . Wherein, the isolation region 202 can be a shallow trench isolation layer; the oxide layer 203 can be silicon dioxide, which is used as a gate oxide layer.

[0020] Please refer to Figure 2b , with hydrogen (H 2 ) and silane (SiH 4 ) after the semiconductor substrate 201 is deposited in the processing chamber, a first polysilicon and amorphous silicon mixed layer 204 will be formed on the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More